Магистраль ISA

| Сдавался/использовался | Апрель/2005г. |

| Загрузить архив: | |

| Файл: ref-21562.zip (103kb [zip], Скачиваний: 51) скачать |

Магистраль ISA была разработана специально для персональных компьютеров типа IBMPCAT (начиная с процессора i80286) и является фактическим стандартом для всех изготовителей этих компьютеров. В то же время отсутствие официального международного статуса магистрали ISA (она не утверждена в качестве стандарта ни одним международным комитетом по стандартизации) она долго использовалась на данных компьютерах как основная шина для подключения внешних устройств. В современных компьютерах используются другие более быстрые шины, но они более сложные и разработка устройств сопряжения для них требует совершенно другого подхода.

ISA явилась расширением магистрали компьютеров IBMPCXT. В ней было увеличено количество разрядов адреса и данных, увеличено число линий аппаратных прерываний и каналов ПДП, а также повышена тактовая частота. К 62-контактному разъёму прежней магистрали был добавлен 36-контактный новый разъём. Тем не менее, совместимость была сохранена, и платы, предназначенные для IBMPCXT, годятся и для IBMPCAT. Характерное отличие ISA состоит в том, что её тактовый сигнал не совпадает с тактовым сигналом процессора, как это было в XT, поэтому скорость обмена по ней не пропорциональна тактовой частоте процессора.

Магистраль ISA относится к демультиплексированным (то, есть имеющим раздельные шины адреса и данных) 16-разрядным системным магистралям среднего быстродействия. Обмен осуществляется 8- и 16-разрядными данными. На магистрали реализован раздельный доступ к памяти компьютера и к устройствам ввода/вывода. Для раздельного доступа имеются специальные сигналы. Максимальный объём адресуемой памяти составляет 16 Мбайт, обеспечиваемый 24-мя адресными линиями. Максимальное адресное пространство для устройств ввода/вывода – 64 Кбайта, обеспечивается 16-ю адресными линиями, хотя практически все выпускаемые платы расширения используют только 10 адресных линий (1 Кбайт). Магистраль поддерживает регенерацию динамической памяти, радиальные прерывания и прямой доступ к памяти. Допускается также захват магистрали.

Наиболее распространенное конструктивное исполнение магистрали – разъёмы (слоты), установленные на материнской плате компьютера, все одноименные контакты которых соединены между собой, то есть все разъёмы абсолютно равноправны. Особенностью конструктивного решения магистрали является то, что платы расширения (дочерние платы), подключаемые к её разъёмам, могут иметь самые различные размеры (длина платы ограничена снизу размером разъёма, а сверху – длиной корпуса компьютера). Платы расширения имеют интерфейсные разъёмы магистрали, выполненные печатными проводниками. Количество установочных мест для плат расширения зависит от типа корпуса компьютера и составляет обычно 2-3 для Utra-slimline корпусов, 3-4 для Slimlineкорпусов, 5-6 для Desktopкорпусов,4-5 для Mini-tower корпусов, 5-7 для Midi-towerкорпусов и более 8 для Big-towerкорпусов.

|

С18………….С1 |

|

A31 ……….A1 |

|

D1………….D18 |

|

B1 ………. B31 |

|

Cторона установки элементов |

|

Cторона монтажа |

|

|

||

Разъём магистрали ISAразделён на две части, что позволяет уменьшать размеры 8-разрядных плат расширения, а также использовать платы разработанные для компьютеров IBMPCXT. Внешний вид плат расширения показан на нижеприведённом рисунке.

Теперь рассмотрим, как сигналы используются при обмене по шине ISA и для чего они служат. Сигналы будут описываться как группами, так и по отдельности, так как ISA содержит как шины, которые нужно описывать в группе, так и отдельные сигналы управления, от состояния которых зависит состояние устройства сопряжения и их необходимо рассматривать по отдельности.

SA0…SA19 – фиксируемые адресные разряды (они действительны в течении всего цикла обмена). Используются для передачи 20 младших разрядов адреса памяти и для адресов устройств, ввода/вывода. При обращении к устройствам ввода/вывода действительны только сигналы SA0..SA15 (но практически все платы расширения работают только с SA0…SA9). При регенерации памяти действительны только сигналы SA0..SA7, состояния старших разрядов не определены. Логика всех сигналов положительная. В режиме MASTER эти сигналы вырабатывает устройство, захватившее магистраль. Тип выходных каскадов – три состояния.

LA17…LA23 – не фиксируемые адресные разряды. Используются для адресации памяти и выработки сигнала –MEMCS16. Действительны, только в начале цикла обмена. Исполнитель должен фиксировать их по отрицательному фронту сигнала BALE. При обращении к устройствам ввода/вывода эти сигналы имеют уровень логического нуля. Логика положительная. Тип выходного каскада – три состояния. Для фиксации необходимо использовать регистр типа “защёлка” (с записью по уровню), стробируемый по сигналу BALE. При прямом доступе к памяти эти сигналы действительны в течении всего цикла обмена, как и SA0…SA19. В режиме MASTERэти сигналы вырабатывает устройство, захватившее магистраль. Тип выходных каскадов – три состояния.

BALE – (BusAddressLatch Enable– разрешение защёлкивания адреса) – сигнал стробирования адресных разрядов. Его отрицательный фронт соответствует действительности адреса на линиях SA0…SA19 и LA17…LA23. Может использоваться устройствами ввода/вывода для заблаговременной подготовки к предстоящему обмену информацией(применяется редко). Тип выходного каскада - ТТЛ.

-SBHE – (System BusHighEnable – разрешение старшего байта) – определяет тип цикла передачи данных (8- или 16- разрядный). Вырабатывается параллельно с сигналами SA0…SA19 и может рассматриваться как дополнительный разряд адреса. Становится активным при передаче старшего байта или 16- разрядного слова (определяется сигналом SA0), пассивен при передаче младшего байта. В режиме MASTERисточником этого сигнала является устройство, которое захватило магистраль. Тип Выходного каскада – три состояния.

SD0…SD15 – разряды данных. По линиям SD0…SD7 передаётся младший байт, по линиям SD8…SD15 – старший байт. Обмен данными с 8- разрядными платами расширения осуществляется по линиямSD0…SD7. Устройство может активизировать шину данных, если к нему идет обращение с циклом чтения или если оно захватило магистраль (в режиме MASTER). Логика сигналов положительная. Тип выходных сигналов – три состояния.

-SMEMR, -MEMR(Memory Read – чтение памяти) – стробы чтения данных из памяти. Память должна выставлять данные при активации этих сигналов. Сигнал –SMEMR вырабатывается только при обращении к адресам, не превышающим FFFFF (в пределах 1 Мбайта), сигнал –MEMR– при обращении ко всем адресам. В режиме MASTER эти сигналы вырабатывает устройство, захватившее магистраль. Тип выходных каскадов – три состояния.

-SMEMRW, -MEMW(MemoryWrite – запись памяти) – стробы записи данных в память. Память должна принимать данные по положительному (заднему) фронту этих сигналов. Сигнал –SMEMW вырабатывается только при обращении к адресам, не превышающим FFFFF(в пределах 1 Мбайта), сигнал –MEMW – при обращении ко всем адресам. В режиме MASTER эти сигналы вырабатывает устройство, захватившее магистраль. Тип выходных каскадов – три состояния.

-IOR (I/ORead) – строб чтения данных из устройств ввода/вывода. Устройство ввода/вывода должно выставлять свои данные при активации сигнала –IOR и снимать их при снятии-IOR. В режиме MASTER этот сигнал вырабатывает устройство, захватившее магистраль. Тип выходных каскадов – три состояния.

-IOW(I/OWrite) – строб записи данных в устройства ввода/вывода. Устройство ввода/вывода должно принимать данные по положительному (заднему) фронту сигнала –IOW. В режиме MASTER этот сигнал вырабатывает устройство, захватившее магистраль. Тип выходных каскадов – три состояния.

-MEMCS16 (MemoryCycleSelect – выбор цикла для памяти) – сигнал выставляется задатчику о том. Что она имеет 16-разрядную организацию. При отсутствии этого сигнала выполняется 8-разрядный обмен. Сигнал врабатывается при распознавании памятью своего адреса на линиях LA17…LA23. Процессор фиксирует его по заднему фронту сигнала BALE. Тип выходного каскада – открытый коллектор.

-I/OCS16 (I/OCycleSelect– выбор цикла для устройства ввода/вывода) – сигнал выставляется устройством ввода/вывода для сообщения задатчику о том, что оно имеет 16-разрядную организацию. При отсутствии этого сигнала выполняется 8-разрядный обмен. Сигнал врабатывается при распознавании устройством ввода/вывода своего адреса на линиях SA0…SA15. Тип выходного каскада – открытый коллектор.

I/OCHRDY ( I/OChannelReady – готовность канала ввода/вывода) – сигнал снимается (делается низким) исполнителем (устройством ввода/вывода или памятью) по переднему фронту сигналов –IOR и –IOW в случае, если он не успевает выполнить требуемую операцию в темпе задатчика. При этом реализуется асинхронный обмен. Если исполнитель успевает работать в темпе задатчика, то сигнал не снимается (фактически не устанавливается в низкий уровень). Цикл обмена в ответ на снятие этого сигнала продлевается на целое число периодов сигнала SYSCLK. Сигнал I/OChannelReady не должен сниматься на время, большее заданного в данном компьютере (по стандарту 15 мкс), иначе компьютер переходит к обработке не маскируемого прерывания. Тип выходного каскада – открытый коллектор.

I/OCHCK( I/OChannelCheck – проверка канала ввода/вывода) – сигнал вырабатывается любым исполнителем (устройством ввода/вывода или памятью) для информирования задатчика о фатальной ошибке, например об ошибке четности при доступе к памяти.

-REFRESH (Refresh — регенерация) — сигнал выставляется контроллером регенерации для информирования всех устройств на магистрали о выполнении циклов регенерации динамического ОЗУ компьютера (каждые 15 мкс). При регенерации выполняется псевдочтение из одного из 256 адресов ОЗУ (активизируются только разряды адреса SA0...SA7). Полный цикл регенерации — около 4 мс. Тип выходного каскада — открытый коллектор.

RESETDRV (Reset ofDriver — сброс устройства) — сигнал сброса в начальное состояние всех устройств на магистрали. Вырабатывается центральным процессором при включении или сбое питания, а также при нажатии на кнопку RESET компьютера. Внешние платы должны в ответ на этот сигнал (длительностью не менее 1 мс) перевести все свои выходы в высокоимпедансное состояние. Тип выходного каскада — ТТЛ.

SYSCLK(SystemClock — системный такт) — сигнал системного тактового генератора со скважностью 2 (меандр). В большинстве компьютеров его частота равна 8 МГц независимо от тактовой частоты процессора. Если в программе SETUP предусмотрена возможность изменения тактовой частоты магистрали, пользователь может задавать ее в широких пределах. Но для обеспечения наибольшей совместимости со всеми имеющимися платами расширения ISA не рекомендуется поднимать эту частоту выше 8 МГц. К тому же на производительность новых компьютеров в целом она влияет незначительно. В компьютерах XT сигнал SYSCLK — это тактовый сигнал процессора. Тип выходного каскада — три состояния.

OSC— не синхронизированный с SYSCLK сигнал кварцевого генератора с частотой 14,31818 МГц со скважностью 2. Может использоваться платами расширения в качестве тактового сигнала, так как его частота одинакова для всех компьютеров с магистралью ISA. Тип выходного каскада — ТТЛ.

IRQ(InterruptRequest — запрос прерывания) — сигналы запроса радиальных прерываний. Запросом является положительный переход на соответствующей линии IRQ. Сигнал должен удерживаться до начала обработки процессором запрошенного прерывания. Тип выходного каскада — ТТЛ. На каждой линии IRQ должен быть один выход. Иногда в литературе можно встретить рекомендацию применять выходы с тремя состояниями, но все равно больше одного выхода на линию быть не должно во избежание конфликтов сигналов. Многие входы IRQ заняты системными ресурсами компьютера (табл. 1.7). Сигналы IRQ0...IRQ2, IRQ8 и IRQ13 задействованы на системной плате и недоступны платам расширения. В компьютере используются два 8-разрядных контроллера прерываний. Сигналы IRQ0...IRQ7 относятся к первому из них, aIRQ8...IRQ15 — ко второму. Для каскадирования второго контроллера прерываний задействован вход IRQ2. В связи с этим запросы прерывания имеют следующие приоритеты в порядке возрастания: IRQ7, IRQ6, IRQ5, IRQ4, IRQ3, IRQ15, IRQ14, IRQ12, IRQ11, IRQ10, IRQ9.DRQ(DMARequest — запрос ПДП) — сигналы запросов прямого доступа к памяти (ПДП). Запросом является положительный переход на соответствующей линии DRQ. Сигнал должен удерживаться до получения ответного сигнала -DACK с тем же номером. Тип выходного каскада — ТТЛ. На каждой линии DRQ должен быть один выход. В компьютере используются два контроллера ПДП. Каналы ПДП, соответствующие первому контроллеру (сигналы DRQ0...DRQ3) предназначены для 8-битного обмена, а соответствующие второму котроллеру (DRQ5...DRQ7) — для 16-битного. Канал DRQ4 используется для каскадирования контроллеров и недоступен пользователям. DRQ0 имеет наивысший приоритет, DRQ7 — наинизший. В IBMPCXTканал DRQ0 использовался для регенерации динамической памяти. Канал DRQ1 зарезервирован для контроллера бисинхронного обмена SDLC, а канал DRQ2 — для контроллера гибкого диска.

|

Номер прерывания IRQ |

INT |

Назначение |

|

0 |

08h |

Программируемый таймер |

|

1 |

09h |

Контроллер клавиатуры |

|

2 |

0Ah |

Каскадирование второго контроллера |

|

8 |

70h |

Часы реального времени (только AT) |

|

9 |

71h |

Программно переадресовано на IRQ2 |

|

10 |

72h |

Резерв |

|

11 |

73h |

Резерв |

|

12 |

74h |

Резерв |

|

13 |

75h |

Математический сопроцессор |

|

14 |

76h |

Контроллер жесткого диска |

|

15 |

77h |

Резерв |

|

3 |

0Bh |

Последовательный порт COM2 |

|

4 |

0Ch |

Последовательный порт СОМ1 |

|

5 |

0Dh |

Параллельный порт LPT2 |

|

6 |

0Eh |

Контроллер гибкого диска |

|

7 |

0Fh |

Параллельный порт LPT1 |

Таблица 2. Назначение аппаратных прерываний ISA.

-DACK(DMAAcknowledge — подтверждение ПДП) — сигналы подтверждения предоставления прямого доступа. Вырабатываются в ответ на соответствующий сигнал DRQ в случае, если прямой доступ предоставлен данному каналу. Удерживаются до окончания прямого доступа. Тип выходного каскада — ТТЛ.

AEN(AddressEnable — разрешение адреса) — используется в режиме ПДП для сообщения всем платам расширения, что производится цикл ПДП. Устанавливается и снимается параллельно с адресом. При его переходе в активное состояние все платы расширения, не участвующие в данном ПДП, должны отключаться от магистрали (переходить в пассивное состояние). Тип выходного каскада — ТТЛ.

Т/С (TerminalCount — окончание счета) — устанавливается в режиме ПДП тогда, когда по текущему каналу ПДП закончен счет циклов пересылок данных. Тип выходного каскада — ТТЛ.

-MASTER(Master — хозяин, задатчик) — используется платой расширения, желающей стать задатчиком магистрали. В этом случае надо выставить сигнал DRQ и, получив в ответ сигнал -DACK, установить сигнал -MASTER, а затем через минимум один период SYSCLK можно выставлять адрес и через минимум два периода SYSCLK можно вырабатывать стробы обмена. Если -MASTER удерживается более 15 мкс, то динамическое ОЗУ компьютера требует регенерации (разрешения сигнала -REFRESH). Тип выходного каскада — открытый коллектор.

Стандартом магистрали ISA установлены ограничения на максимальное значение тока, потребляемого каждой платой расширения (они связаны только с возможностями используемого разъема). Значения этих токов для всех напряжений питания приведены в таблице 1.8. Отметим, что максимальный ток потребления всеми используемыми платами расширения определяется типом источника питания данного компьютера и не стандартизован. Вообще же мощность блока питания зависит от класса компьютера и может варьироваться от 100—150 Вт (для slim-корпусов) до 300—330 Вт (для big-tower). Некоторые современные «зеленые» компьютеры имеют блоки питания с мощностью не более 75 Вт. Но наиболее типичные параметры источника питания IBMPCAT мощностью 200 Вт приведены в таблице 1.9.

|

Напряжение |

8-разрядная плата (XT) |

16-разрядная плата |

|

+5 В |

3,0 А |

4,5 А |

|

-5 В |

1,5А |

1,5А |

|

+12 В |

1,5А |

1,5А |

|

-12В |

1.5А |

1,5А |

Таблица 3. Максимальныетокипотребленияплатамирасширения.

|

Напряжение питания источника |

Допустимый ток нагрузки |

|

+5В |

7.0...19.8А |

|

-5 В |

0,0...0,3 А |

|

+ 12В |

2,5...7,ЗА |

|

-12 В |

0,0...0,ЗА |

Таблица 4. Допустимыетокипотребленияотисточникапитания.

Выходные напряжения источника достигают номинального уровня за время не более 100 мс после включения питания. Источники, как правило, имеют встроенную защиту от перегрузок, которая включается за время 20 мс. Источник должен быть обязательно нагружен по напряжениям +5 В и +12 В. Если по этим выходам не будет обеспечен минимальный ток потребления, это воспринимается как перегрузка. Для выхода из перегрузки надо выключить и снова включить питание источника через время не менее 1с.

Циклы магистрали ISA

В режиме программного обмена информацией на магистрали ISA выполняются четыре типа циклов:

♦ цикл записи в память;

♦ цикл чтения из памяти;

♦ цикл записи в устройство ввода/вывода;

♦ цикл чтения из устройства ввода/вывода.

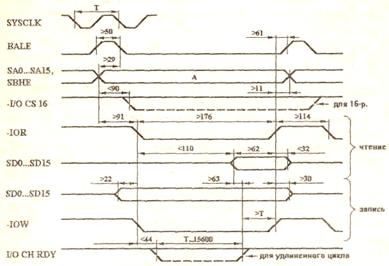

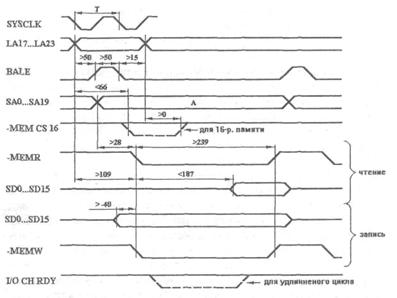

Наиболее часто УС проектируются как устройства ввода/ вывода. Временные диаграммы циклов обмена для этого случая приведены на рис. 1.3 (все временные параметры приведены для частоты SYSCLK, равной 8 МГц). Циклы начинаются с выставления задатчиком адреса на линиях SA0...SA15 и сигнала -SBHE. Отметим, что несмотря на потенциальную возможность адресации по 16 линиям адреса, чаще всего используются только 10 младших линий SA0...SA9, так как большинство разработанных ранее плат расширения используют только их, и, следовательно, за исключением особых случаев нет смысла обрабатывать старшие разряды SA10...SA15. Это будет подробнее рассмотрено в главе 2. В

Рис. 1.3. Временныедиаграммыцикловпрограммногообмена сустройствамиввода/вывода (всевременныеинтервалы внаносекундах).

ответ на получение адреса исполнитель, распознавший свой адрес, должен сформировать сигнал -I/OCS16 в случае, если обмен должен быть 16-разрядным.

Далее следует собственно команда чтения или записи. При цикле чтения задатчик выставляет сигнал -IOR, в ответ на который исполнитель (УС) должен выдать данные на шину данных. Эти данные должны быть сняты исполнителем после окончания сигнала -IOR. В цикле записи задатчик выставляет записываемые данные и сопровождает их стробом записи -IOW. Здесь надо отметить, что хотя в соответствии со стандартом установка записываемых данных предшествует выставлению -IOW, в некоторых компьютерах реализуется обратный порядок: сначала выставляется -IOW, а затем появляются данные. Поэтому при проектировании УС надо рассматривать как момент действительности данных только задний (положительный) фронт сигнала -IOW.

В случае, когда УС не успевает выполнить требуемую от него команду в темпе магистрали, оно может приостановить на целое число периодов сигнала SYSCLK завершение цикла чтения или записи с помощью снятия (перевода в низкий уровень) сигнала I/OCHRDY (так называемый удлиненный цикл). Это производится в ответ на получение сигнала -IOR или -IOW. Сигнал I/OCHRDY может удерживаться низким не более 15,6 мкс, в противном случае процессор переходит в режим обработки немаскируемого прерывания. Отметим, что некоторые изготовители персональных компьютеров указывают в сопроводительной документации другие допустимые величины этого временного интервала (например, 2,5 мкс), так что не следует ориентироваться на максимальную величину, указанную в стандарте, иначе нет гарантии работы УС во всех компьютерах.

На рис. 1.4 приведены временные диаграммы циклов обмена с памятью (указаны только временные интервалы, отличающиеся от аналогичных на рис. 1.3). Для асинхронного режима обмена (удлиненного цикла) здесь также используется сигнал I/O CHRDY. Отметим, что УС, работающее как память, должно обрабатывать все адресные разряды, включая LA17...LA23.

Помимо циклов программного обмена на магистрали ISA могут выполняться также циклы прямого доступа к памяти

Рис. 1.4. Временныедиаграммыцикловпрограммногообмена спамятью (всевременныеинтервалывнаносекундах).

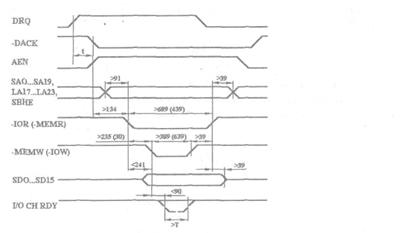

Рис. 1.5. ВременныедиаграммыцикловПДП (t—время предоставленияПДП, Т—периодсигналаSYSCLK; все временныеинтервалывнаносекундах).

(ПДП). Временная диаграмма для этого случая показана на рис. 1.5. Так как магистраль ISA имеет раздельные стробы чтения и записи для устройств ввода/вывода и для памяти, пересылка данных в режиме ПДП производится за один машинный цикл. То есть если данные надо переслать из устройства ввода/вывода в память, то одновременно производится чтение данных из устройства ввода/вывода (по сигналу -IOR) и их запись в память (по сигналу -MEMW). Аналогично производится пересылка данных из памяти в устройство ввода/вывода (по сигналам -MEMR и -IOW).

Цикл ПДП начинается с запроса ПДП от исполнителя, желающего произвести обмен, с помощью одного из сигналов DRQ. После освобождения магистрали текущим задатчиком (например, процессором) контроллер ПДП формирует соответствующий сигнал -DACK, говорящий о предоставлении ПДП запросившему его устройству. Затем контроллер ПДП вырабатывает адрес ячейки памяти, с которой будет производиться обмен в текущем цикле, и сигнал AEN, который говорит устройству ввода/вывода о том, что к нему идет обращение в режиме ПДП. После этого выставляется строб чтения (-IOR или -MEMR), в ответ на который источник передаваемых данных выставляет свою информацию на шину данных, и строб записи (-MEMW или -IOW), по которому данные записываются в приемник данных. Здесь так же, как и в обычном цикле возможен асинхронный обмен (удлиненный цикл) с использованием сигнала I/OCHRDY.

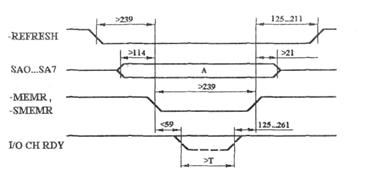

Одной из особенностей магистрали ISA является необходимость проведения регенерации динамической памяти компьютера с помощью специальных циклов регенерации на магистрали. Временная диаграмма цикла регенерации показана на рис. 1.6. Эти циклы выполняет входящий в состав материнской платы компьютера контроллер регенерации, который должен для этого получать управление магистралью каждые 15 микросекунд. Во время цикла регенерации производится чтение одной из 256 ячеек памяти (для адресации используются только восемь младших разрядов адреса SA0...SA7). При этом читаемая информация нигде не используется, то есть это цикл псевдочтения. Проведение 256 циклов регенерации, то есть псевдочтение из 256 последовательных адресов ОЗУ, обеспечивает полное освежение информации в ОЗУ и ее непрерывное сохранение. Если по каким-то причинам цикл регенерации не производится вовремя, то возможна утеря информации в ОЗУ. Цикл регенерации включает в себя выставление сигналов -REFRESH, адреса SA0...SA7 и -MEMR. В случае необходимости может использоваться сигнал I/OCHRDY.

Рис. 1.6. Временныедиаграммыцикловрегенерации (Т—период сигналаSYSCLK, всевременныеинтервалывнаносекундах).

1.2.4. Электрические характеристики линий ISA

При проектировании УС помимо протоколов обмена по магистрали надо учитывать также электрические характеристики сигналов. Стандарт магистрали определяет требования к входным и выходным токам приемников и источников сигнала каждой из плат расширения. Несоблюдение этих требований может нарушить функционирование всего компьютера и даже вывести его из строя.

Выходные каскады передатчиков магистральных сигналов УС должны выдавать ток низкого уровня не меньше 24 мА (это относится ко всем типам выходных каскадов), а ток высокого уровня—не меньше 3 мА (для выходов с тремя состояниями и ТТЛ).

Входные каскады приемников магистральных сигналов должны потреблять входной ток низкого уровня не больше 0,8 мА, а входной ток высокого уровня — не больше 0,04 мА.

Кроме этого необходимо учитывать, что максимальная длина печатного проводника от контакта магистрального разъема довывода микросхемы не должна превышать 65 миллиметров, а максимальная емкость относительно земли по каждому контакту магистрального разъема не должна быть больше 20 пФ.

К некоторым линиям магистрали подключены нагрузочные резисторы, идущие на шину питания +5 В. К линиям -IOR, -IOW, -MEMR, -MEMW, -SMEMR, -SMEMW, -I/O СН СК подключены резисторы 4,7 кОм, к линиям -I/OCS 16, -MEMCS 16, -REFRESH, -MASTER, -OWS - 300 Ом, а к линии I/O СН RDY — 1 кОм. Кроме того, к некоторым линиям магистрали подключены последовательные резисторы: к линиям -IOR, -IOW, -MEMR, -MEMW, -SMEMR, -SMEMW и OSC - резисторы номиналом 22 Ом, а к линии SYSCLK — 27 Ом.