Конспект лекций по курсу "Микропроцессоры и микро-ЭВМ в Персональной электронике" для студентов специальности 2008

| Загрузить архив: | |

| Файл: ref-30853.zip (826kb [zip], Скачиваний: 372) скачать |

МИНИСТРЕРСТВО ВЫСШЕГО ОБРАЗОВАНИЯ РФ

МОСКОВСКАЯ ГОСУДАРСТВЕННАЯ АКАДЕМИЯ ПРИБОРОСТРОЕНИЯ И ИНФОРМАТИКИ

КАФЕДРА "ПЕРСОНАЛЬНАЯ ЭЛЕКТРОНИКА"

Конспект лекций по курсу "Микропроцессоры и микро-ЭВМ в Персональной электронике" для студентов специальности 2008

Москва 2001

ВВЕДЕНИЕ. ПОНЯТИЕ О МИКРОПРОЦЕССОРАХ

В последнее десятилетие наметилась четкая тенденция повышения роли вычислительной техники во всей жизни современного человека. Недаром в наших школах введено преподавание нового предмета "Основы информатики и вычислительной техники".

Наряду с бурным развитием вычислительной техники еще наблюдается две глобальные тенденции в современной радиоэлектронике. Во-первых, усложняются функции любого электронного аппарата. При этом с точки зрения эксплуатации его, наблюдается упрощение работы с ним даже необученного пользователя. Во-вторых, радиоэлектроника расширяет свое влияние на все большие сферы человеческой деятельности. Теперь ее применение наблюдается даже в тех областях, в которых ранее ее использование казалось немыслимым. Эти два аспекта можно назвать усилением "интеллектуализации" техники.

Из этого вытекает еще одна реалия современного развития электроники - крен в сторону техники, направленной на удовлетворение "бытовых" потребностей человека. Поэтому в самое последнее время получил развитие термин "Персональная электроника", который имеет в виду не только электронику для "домашнего использования", а и офисную, автомобильную и другие виды устройств, которые направлены на удовлетворение персональных потребностей пользователя.

Все указанные выше тенденции и особенности применения электроники были бы невозможны без поистине взрывоподобного развития микропроцессорной техники. Начало ее использования было весьма скромным, а сейчас ни один мало-мальски сложный аппарат не может без нее обойтись. Благодаря своим преимуществам микропроцессорная техника начинает вытеснять традиционную радиоэлектронику из такого понятия, как элементная база.

Естественно, теперь при обучении проектированию персональной электроники нельзя не давать студентам хотя бы основ применения микропроцессорной техники. Поэтому не вызывает сомнения актуальность преподавания курса "Применение микропроцессоров и микро-ЭВМ в Персональной электронике" студентам специальности "Персональная электроника" (2008).

Целью настоящего курса является дать понятие о микропроцессорах и однокристальных микро-ЭВМ, области их применения, дать основы функционирования микропроцессорных систем, научить основам программирования микропроцессоров и микро-ЭВМ, построения простейших систем управления объектами.

Курс состоит из лекционных и практических занятий и лабораторного практикума. Он построен таким образом, чтобы на лекциях дать слушателям наиболее широкое представление о предмете, а на практических и лабораторных занятиях познакомить их с конкретными микропроцессорными системами, научить основам построения и функционирования определенных систем управления на основе одного - двух наиболее популярных микропроцессорных наборов.

После окончания обучения слушатель должен свободно ориентироваться в многочисленной литературе по микропроцессорам и микро-ЭВМ, уметь выбрать тот или иной микропроцессорный комплект для использования в конкретной системе, уметь программировать один из самых распространенных микропроцессорных систем, составлять структурную и принципиальную схемы микропроцессорной системы для ее использования в конкретной области техники. В дальнейшем слушатель, основываясь на литературе и материалах о микропроцессорных системах, сможет сам проектировать и, главным образом, уметь применять микропроцессоры в своей повседневной работе, свободно ориентироваться в обслуживании и ремонте такого рода аппаратуры.

История появления микропроцессоров

Появление микропроцессоров обязано слиянию двух ранее независимых отраслей техники. Первая из них - создание систем управления промышленными объектами. В начале 60-х годов функции многих промышленных систем настолько усложнились, что потребовалось создавать сложные автоматические системы управления этими объектами. Эпоха НТР потребовала создания высокоавтоматизированных, быстро переналаживаемых производств, так называемых "гибких автоматизированных производств". Но если применять старую методику переналадки всего машинного парка производства, то это потребовало бы слишком больших затрат на переход с одного вида продукции на другой. Поэтому встала потребность создания таких управляющих устройств-производств, которые бы переналаживались на выпуск другой продукции самыми простыми средствами.

С другой стороны параллельно этим отраслям развивалась мощная база вычислительной техники. На заре своего развития она мало что умела, имела очень большие габариты и главное - низкую надежность из-за использования электронных ламп. Но по мере совершенствования вычислительная техника становилась все более мощной, все менее громоздкой, все более удобной для эксплуатации. Но развитие этой техники шло в основном по пути наращивания мощности и возможности больших ЭВМ, установленных в отдельных, специально приспособленных помещениях, обслуживаемых специально обученным персоналом высокой квалификации. Использование средств вычислительной техники в таком виде для нужд производства имело ограниченный характер.

В это же время в радиоэлектронике (и, в частности, в вычислительной технике) шло естественное развитие элементной базы. На смену лампам пришли транзисторы. Габариты и потребляемая мощность сразу снизились в десятки раз. Но подлинный переворот в радиоэлектронике был совершен, когда появились первые интегральные микросхемы, т.е. тогда, когда внутри пластины полупроводника стали изготовлять готовые схемы, а не отдельные активные приборы. Это позволило существенно снизить габариты, потребляемую мощность, повысить надежность аппаратуры.

Совершенствование технологии изготовления интегральных схем (ИС) привело к появлению ИС средней степени интеграции, (когда на одном кристалле размещалось несколько десятков транзисторов), ИС большой степени интеграции или БИС (когда на кристалле тысячи и десятки тысяч элементов), и наконец, ИС сверхбольшой степени интеграции или СБИС (на кристалле - миллионы элементов). Однако по мере развития элементной базы стало все более очевидным противоречие: если на транзисторах или на ИС малой интеграции можно было построить различную аппаратуру (по своим функциональным возможностям), то по мере роста степени интеграции ИС становились все более специализированными. Действительно, в одной БИС размещалось порой целое устройство, и эту БИС нельзя было применить для построения другого аппарата. Кроме того, хотя и изготовление такой ВИС было достаточно дешевым, но проектирование таких специализированных БИС требовало все больших затрат, а сфера их применения все суживалась. Таким образом, развитие элементной базы вело в тупик.

Подлинной революцией, которая позволила выйти из этого тупика, стало появление микропроцессоров. В 1971 г. фирма Intel (США) выпустило БИС под кодом 4004 и назвала ее микропроцессором. На микроэлектронный уровень была перенесена идеология средств вычислительной техники. Впервые БИС стала именно универсальной системой благодаря сочетанию аппаратных и программных средств. Т.е. структура БИС была неизменной, а универсальность ей придавалось возможностью программирования ее функций. Таким образом, для различных применений требовалось только написать другую программу работы, без изменения структуры микропроцессорной системы.

Но основное применение микропроцессоров сразу открылось именно в построении управляющих систем промышленности. Проектировщики сразу поняли все преимущества новой элементной базы. Теперь требовалось изменять только программу работы оборудования, а все оборудование остается неизменным. И что самое важное, стало возможным встраивать микропроцессоры непосредственно в оборудование, что придало ему еще большую гибкость.

Микропроцессорная техника стала бурно развиваться. Появились микропроцессорные комплекты для построения самых различных систем, и в том числе вычислительных. В настоящее время промышленность выпускает большую номенклатуру микропроцессоров, которые можно применять для построения различных управляющих промышленных систем, для создания достаточно мощных вычислительных систем, и для встраивания в бытовую технику.

Следующим этапом развития элементной базы стало применение однокристальных микро-ЭВМ (ОЭВМ). Действительно, для включения микропроцессора в систему было необходимо предусмотреть "навешивание" на него еще по крайней мере нескольких микросхем - памяти, генераторов, интерфейсных схем и т.д. Все это выливалось в увеличение габаритов, потребляемой мощности, снижение надежности. Поэтому на определенном этапе очевидным решением стало интеграция всех этих устройств на одном кристалле. При этом основные преимущества МП техники сохранились и даже развились дальше. Можно сказать, что в настоящее время "чистые" микропроцессоры применяются только в вычислительной технике, а в персональной электронике подавляющее большинство управляющих систем построено на ОЭВМ.

Сейчас уже можно сказать, что ни одна сторона техники и быта не может обойтись без применения микропроцессоров и ОЭВМ в той или иной мере.

Терминология курса

Для изучения микропроцессорной техники, литературы по этому вопросу необходимо познакомиться с терминологией, встречающейся в различных источниках. В настоящем разделе приводятся только наиболее общие термины. Другие понятия будут расшифрованы в соответствующих разделах.

Микропроцессор (МП) - программно управляемое устройство, предназначенное для обработки цифровой информации и управления процессами этой обработки, и выполненное в виде одной (или нескольких) ИС с высокой степенью интеграции электронных компонентов.

Микропроцессорный комплект (МПК) - совокупность МП и других ИС, совместимых по конструкторско-технологическому исполнению и предназначенных для совместного применения при конструировании МП, микро-ЭВМ, и других управляющих систем.

Микропроцессорная система (МПС) - управляющая, информационная или иная специализированная цифровая система, построенная на базе МП или микро-ЭВМ, включающая в себя средства связи с объектом управления или с пользователем.

Аппаратные средства МПС - МП средства и схемы сопряжения с обслуживаемым объектом, имеющие некоторую конструктивную базу и соединенные согласно определенной принципиальной схеме.

Программные средства МПС - последовательность команд, программа или совокупность программ, размещенных на средствах носителях информации и реализующие требуемый алгоритм ее функционирования.

Однокристальная микро-ЭВМ (ОЭВМ) - МПС, реализованная на одном кристалле, и выполняющая основные функции управления и сопряжения с объектом.

Классификация и основные параметры МП

Сложность классификации МП средств связана с тем, что с одной стороны МП - это функциональное вычислительное устройство, а с другой стороны - это БИС. Поэтому для МП важны такие параметры БИС, как:

тип корпуса БИС,

количество источников питания,

требования к синхронизации,

мощность рассеяния,

температурный диапазон,

быстродействие,

уровни сигналов,

возможность наращивания,

нагрузочная способность и т.д.

Как функциональное устройство МП характеризуется следующими параметрами:

формат обрабатываемых данных,

количество, тип и гибкость системы команд,

методы адресации данных,

число внутренних регистров,

средства прерываний,

построение системы ввода-вывода и т.д.

Как и обычное устройство управления МП можно разделить на три части: операционную (в ней осуществляется преобразование данных), управляющую (осуществляет управление обработкой данных по программе) и интерфейсная (осуществляет связь МП с внешними устройствами). Первые две части характеризуются разрядностью, системой команд, системой прерываний и т.д., третья часть - разрядностью, возможностью подключения других частей системы и т.д.

Конструктивно все три части могут присутствовать в одном кристалле БИС, тогда этот МП называют однокристальным МП: или каждый кристалл МПС выполняет свою функцию - тогда МП называют многокристальным . Ряд МП допускают наращивание до необходимой разрядности, причем отдельно можно наращивать все три части МП. Тогда эти МП называют многокристальными секционированными, где каждая секция обрабатывает свою область разрядов данных. На рис. 0.1 условно показаны эти типы МП.

<

а) б) в)

УП- управляющая часть, ОП - операционная часть, ИП - интерфейсная часть

Рис. 0.1.

Поэтому по числу БИС в МПК МП классифицируются:

-однокристальные,

многокристальные,

многокристальные секционированные.

По назначению:

- универсальные - могут быть использованы для широкого круга задач, причем их эффективность слабо зависит от типа решаемой задачи,

- специализированные - они ориентированы на выполнение определенных функций, что позволяет существенно повысить эффективность при решении определенного класса задач. В частности, это специальные математические процессоры, процессоры обработки видеоданных и т.д. Производительность этих процессоров очень высока, но только для узкого круга решаемых задач.

По виду обрабатываемых данных:

- цифровые,

- аналоговые (МП - цифровые устройства, но на их входах и выходах стоят соответственно аналогово-цифровые и цифро-аналоговые преобразователи).

По виду временной синхронизации:

- синхронные - МП, в которых начало и конец каждой операции задаются устройством управления и не зависят от вида команд и величины операндов,

- асинхронные МП - начало последующей операции определяется по фактическому окончанию предыдущей операции.

По организаций МПС:

- одномагистральная МПС - все устройства системы имеют один интерфейс и подключены к единой магистрали, по которой передаются коды данных, адресов и управляющих сигналов,

- многомагистральная МПС - устройства группами подключаются к своей информационной магистрали, по которым можно осуществить одновременную передачу данных, адресов и управляющих сигналов.

По виду системы команд:

- МП с жестким набором команд - каждая команда такого МП не может быть разделена на более простые операции. Система команд такого МП не может быть изменена программным способом,

- МП с микропрограммированием - система команд такого МП может быть модифицирована за счет изменения последовательности микропрограмм. из которых состоит каждая команда такого МП. Мировая промышленность выпускает в настоящее время большое число МПК. Каждый из них предназначен для определенного применения, имеет свои особенности. Основной вопрос при применении МП средств - выбор определенного МПК. Как видно из предыдущего изложения, параметров МПК много, поэтому в табл. 0.1 указаны основные МПК, выпускаемые отечественной промышленностью, и некоторые особо важные их параметры.

Таблица 0.1

Обозначение серии |

Наименование ЦПЭ |

Технология |

Разрядность, бит |

Тактовая частота, МГц |

Напряжения питания, В |

Потребляемая мощность, мВт |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

К580 |

КР580ВМ80А |

nМОП |

8 |

2,5 |

-5,+5,+12 |

700 |

К584 |

К584ВМ1 |

И2Л |

4п |

0,5 |

+5 |

750 |

К588 |

К588ВС1 |

КМОП |

16п |

0,8 |

+5 |

1,0 |

К589 |

К589ИК02 |

ТТЛШ |

2п |

10,0 |

+5 |

850 |

К1800 |

К1800ВС1 |

ЭСЛ |

4п |

36,0 |

-5,2;-2 |

400 |

К1801 |

К1801ВМ1 |

nМОП |

16 |

5,0 |

+5 |

600 |

К1802

К1804 |

КР1802ВС1 |

ТТЛШ |

8п |

8,0 |

+5 |

800 |

Примечание: при обозначении разрядности символ "n" обозначает возможность кратного наращивания разрядности (секционированные процессоры).

Как видно из табл. 0.1, технология изготовления БИС определяет многие параметры МПК: быстродействие, потребляемую мощность, плотность компоновки на кристалле, напряжения питания и т.п. В таблице указаны универсальные МП.

Как уже упоминалось во Введении, те МП, которые приведены в табл.0.1, уже давно не имеют никаких перспектив по использованию в современной радиоэлектронике. Вместо МП сейчас используются только микроконтроллеры (МК), как называются иначе однокристальные микро-ЭВМ. Ниже приведен краткий обзор современных МК.

1. Обзор современных ОЭВМ

Хотя первыми на рынке появились микропроцессоры (МП), и они в 70-х и 80-х годах были основной элементной базой управляющих и вычислительных устройств, по мере развития микроэлектроники МП были вытеснены из большинства своих применений ОЭВМ, которые иначе еще называются микроконтроллерами (МК). В настоящее время МП сохраняют свое ведущее положение только в вычислительной технике (производство ПЭВМ).

Микроконтроллеры (МК) являются наиболее массовыми представителями современной микропроцессорной техники, объем выпуска которых составляет около 2,5 млрд. штук в год. Имея на своем кристалле высокопроизводительный процессор, память и набор периферийных устройств, МК позволяют с минимальными затратами реализовать высокоэффективные системы и устройства управления различными объектами и процессами. Благодаря этому они находят широкое применение в промышленной автоматике, контрольно-измерительных приборах и системах, аппаратуре связи, автомобильной электронике, бытовой технике и многих других применениях.

Первым МК на рубеже 80-х и 90-х годов стала микросхема той же фирмы INTEL I8048. Она была очень простой, содержала на кристалле всего 1 Кбайт ПЗУ или ППЗУ, могла адресовать всего 4 Кбайт памяти программ, имела только 64 байта ОЗУ на кристалле. Этот тип МК так и не стал массовым и далее не развивался.

Другим, и гораздо более перспективным прибором, стал МК типа I8751. Этот тип МК дал начало целому семейству МК, которое получило название MCS-51. Структура и возможности этого МК были настолько удачными, что это семейство развивается до сих пор. Со временем фирма INTEL отошла от производства МК, но эстафету подхватили такие мощные фирмы, как Philips, Atmel, Dallas Semiconductors, Analog Devices и другие. Они теперь развивают эту ветвь МК.

Еще на заре развития МП в этой отрасли появился такой гигант радиоэлектроники, как американская фирма Motorolla. Она примерно в то же время, что и INTEL начала развивать свою отрасль МП и первым процессором стал МС6800. Он имел несколько иную структуру, чем I8080, хотя по такому интегральному показателю, как "мощность" это были примерно равные приборы. Со временем Motorolla также поняла перспективность развития МК и выпустила на рынок 8-разрядные семейства МК 68НС05. И в настоящее время продукция фирмы контролирует значительную часть рынка МК.

Основным недостатком МК еще недавно была их относительно высокая стоимость. Это не позволяло эффективно использовать их в простых приложениях, где надо было считать каждую копейку, а задачи, возложенные на МК были самыми простыми.

Поэтому возникла идея создать наиболее простой, но и наиболее дешевый процессор.

Поэтому фирма Microchip разработала целое семейство МК, основанных на так называемой RISC технологии. Основной особенностью ее является упрощенная система команд, состоящая, как правило, из нескольких десятков простейших инструкций. На этой основе были созданы PIC МК. Со временем они, конечно, усложнились, их мощность повысилась, но они и сейчас остались самыми дешевыми и простыми МК.

Таким образом, можно констатировать, что рынок МК сейчас поделен на 3 части: семейство MCS-51 (примерно 50 - 60%), МК фирмы Motorolla (20 - 30%) и PIC МК (10 - 20%).

Ниже приводятся краткие сведения о последних двух видах МК, а контроллеры семейства MCS-51 рассматриваются более подробно в разделе ???.??., а МК типа PIC - в разделе ??????.

1.1. МИКРОКОНТРОЛЛЕРЫ ФИРМЫ MOTOROLLA

МК фирмы MOTOROLLA составляют несколько семейств, которые различаются в основном по вычислительной мощности и ориентации на определенные области применения.

В первую очередь это 8-разрядные МК семейств НС05, НС08 и НС11.

Семейство 68НС05 содержит более 150 модификаций МК, которые формировались фирмами, использующими аппаратуру на контроллерах, или так называемые "заказные" МК. Они настроены под конкретную конфигурацию программно-аппаратных средств пользователя.

МК МС68НС08 - развитие семейства НС05. Они совместимы по системе команд и коду с этими МК, но имеют в 5 - 10 раз большую производительность. МК этого типа имеют модульную внутреннюю архитектуру, большую универсальность, увеличенные объемы внутренней памяти, энергонезависимые блоки памяти типа EEPROM Flash EEPROM.

Семейство МС68НС11 ориентировано на массовое применение и характеризуется большей гибкостью и универсальностью, широким применением внешней памяти. Ядро системы усовершенствовано, отличается повышенной производительностью и более эффективной архитектурой и системой команд. В семейство входят более 40 модификаций МК.

1.1.1. Семейство НС05

Все МК этого семейства имеют одинаковое 8-разрядное процессорное ядро, основанное на известном процессоре 6800, и отличаются набором периферийных функций. Это означает, что применение любого МК этого семейства позволяет пользователю использовать единый подход к проектированию системы на МК НС05, а также на МК НС08, который основан на более производительном, но программно совместимом ядре.

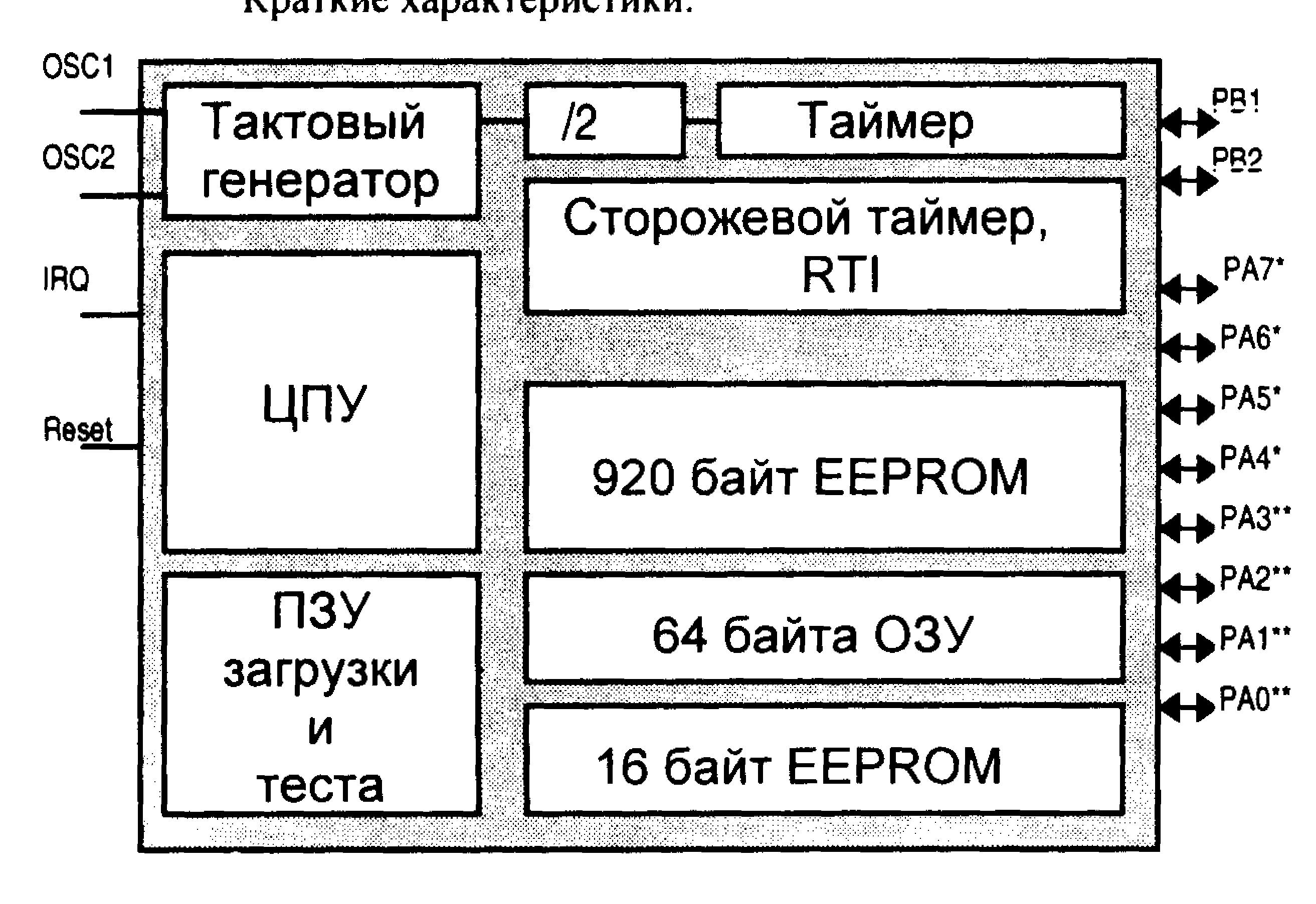

<

Примером построения системы НС05 служит МК МС68НС805К3, предназначенный для работы в системах, требующих использование малогабаритного МК с микропотреблением и низкой стоимостью: охранных системах, датчиках, бытовых устройствах, портативных средствах связи, пультах дистанционного управления. Основные характеристики МК следующие:

ЦПУ НС05, умножение 8х8,

питание от 1,8 В (запись EEPROM от 3 В), низкое потребление,

920 + 16 Кбайт EEPROM,

прерывания реального времени,

прерывания от клавиатуры по 8 линиям,

нагрузочная способность до 8 мА по четырем линиям,

режимы пониженного потребления STOP, WAIT.

Структурная схема МК показана на рис.1.2.

<

>

Рис. 1.2. Структурная схема МК МС68НС805К3

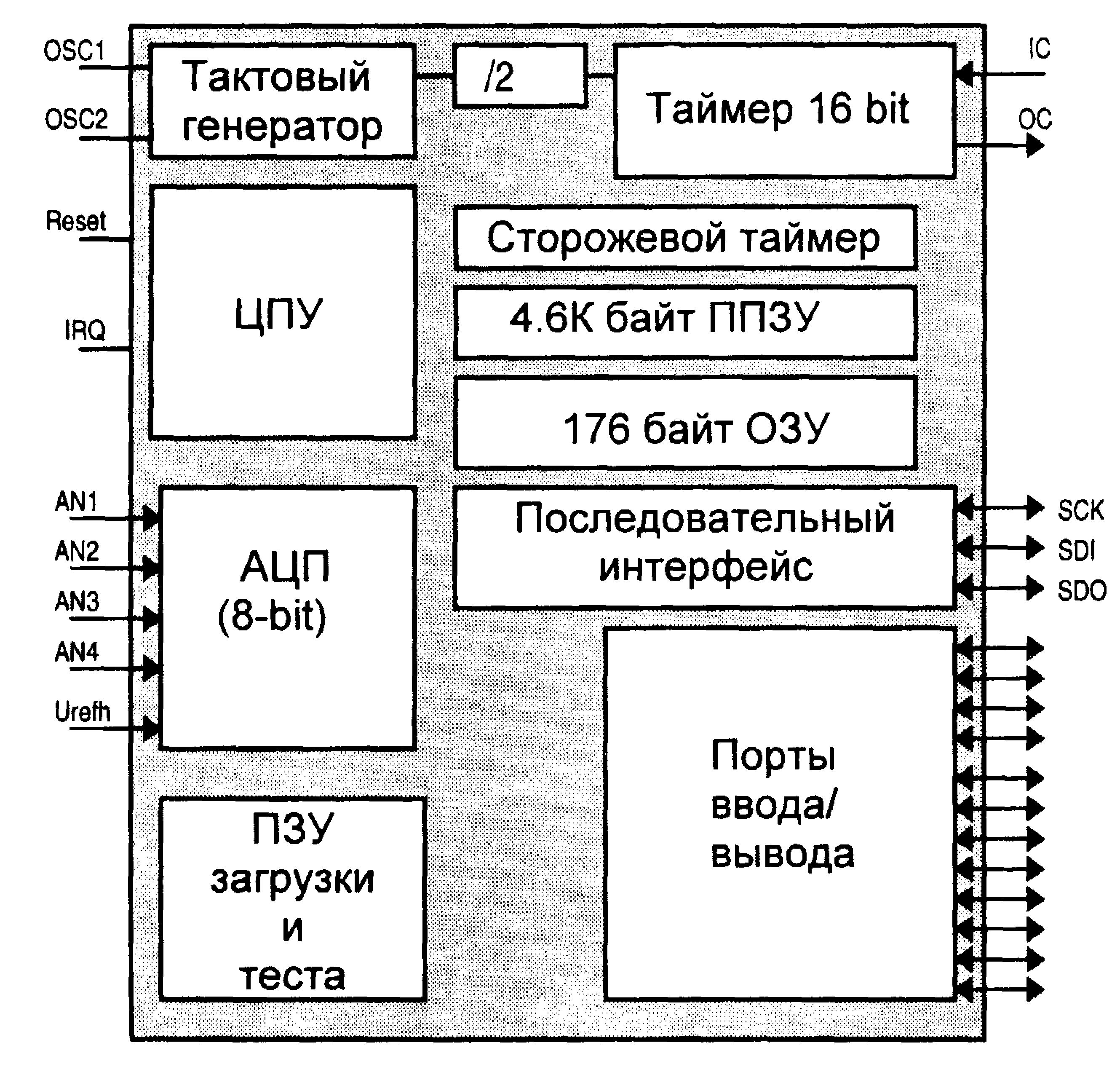

Второй пример - МК типа МС68НС705Р6А, который может применяться в устройствах, требующих обработки аналогового сигнала и критичных к габаритам и стоимости применяемого МК, например, устройствах контроля температуры, электронных весах, локальных узлах управления, устройствах сигнализации, средствах связи и т.д.

Основные характеристики МК следующие:

ЦПУ НС05, умножение 8х8,

АЦП ( 4 канала, 8 разрядов),

синхронный последовательный порт,

16-разрядный таймер с функциями входного захвата и выходной фиксации,

4,6 Кбайт ППЗУ,

176 байт ОЗУ,

21 линия ввода-вывода,

прерывания от 8 линий,

2 выхода с током 15 мА,

режимы пониженного потребления STOP, WAIT, сохранение данных в ОЗУ

Структурная схема МК показана на рис.1.3.

1.1.2. Семейство НС08

Семейство НС08 является следующим шагом в развитии МК и характеризуется повышенной в 5 - 10 раз производительностью процессорного ядра, совместимого по системе команд с ЦПУ НС05. Оно поддерживает дополнительные команды и способы адресации, а также новые функции - ПДП, технологию "нечеткой логики" и элементы цифровой обработки сигналов.

Ядро ЦПУ полностью статическое и оптимизировано для работы с пониженным напряжением питания и с помощью встроенного синтезатора частоты позволяет гибко управлять потреблением. Это первое семейство МК с определяемым пользователем архитектурой на базе стандартных модулей, что ускоряет цикл разработки системы.

Основные модули системы рассматриваются ниже.

<

>

Рис. 1.3. Структурная схема МК МС68НС705Р6А

Особенностями ЦПУ (логическая модель его показана на рис. 1.4) НС08 являются:

тактовая частота 8 МГц (цикл 125 нс),

16-разрядные индексный регистр, программный счетчик, указатель стека,

<

Рис. 1.4. Структура ЦПЭ семейства НС08

8 методов адресации, включая операции с индексным регистром и стеком, а также пересылки память-память,

аппаратная поддержка ПДП, точек останова,

быстрые операции умножения и деления,

64 Кбайт адресуемой памяти с возможностью расширения,

полностью статическая архитектура, низкое потребление, пониженное питание.

Модуль прямого доступа в память (DMA08) обеспечивает скоростной обмен с памятью и внешними устройствами. Он может обслуживать последовательный интерфейс, либо обеспечивать передачу блоков данных до 256 Кбайт.

Модуль таймера (TIM08) - устройство для решения задач, связанных с обработкой временных интервалов. Может иметь 2, 4 и 6 независимых каналов, каждый из которых содержит 16-битовый счетчик с программируемым предделителем, регистры входной фиксации, выходного сравнения и ШИМ.

Модуль последовательного обмена представлены универсальным асинхронным интерфейсом (SCI08), универсальным синхронным интерфейсом (SPI08),специализированными последовательными интерфейсами, применяемыми в автомобильных системах и системах промышленного управления.

Модуль системной интеграции (SIM08) - его основные функции:

формирование внутренней тактовой частоты процессора и встроенных подсистем,

обеспечение режимов пониженного энергопотребления и программное управление частотой,

управление прерываниями и сбросом - сигнал сброса при обнаружении неправильных кодов команд и адресов, работа сторожевого таймера, обработка и арбитраж программных и аппаратных прерываний.

Встроенная память может состоять из масочного или программируемого ПЗУ, ЭСППЗУ (EEPROM и Flash EEPROM), ОЗУ.

Модуль управления ЖКИ дисплеем (LCD08) позволяет подключать до 1280 сегментов (32 группы по 40 сегментов) и содержит внутреннее буферное ОЗУ 160 байт, формирователь напряжений для драйверов, регулировка контрастности.

АЦП (ADC08),

12-разрядный 6 канальный контроллер ШИМ (PWM08),

таймер периодических прерываний (PIT08).

модуль расширения адресации внешней памяти до 16 Мбайт (ADX08).

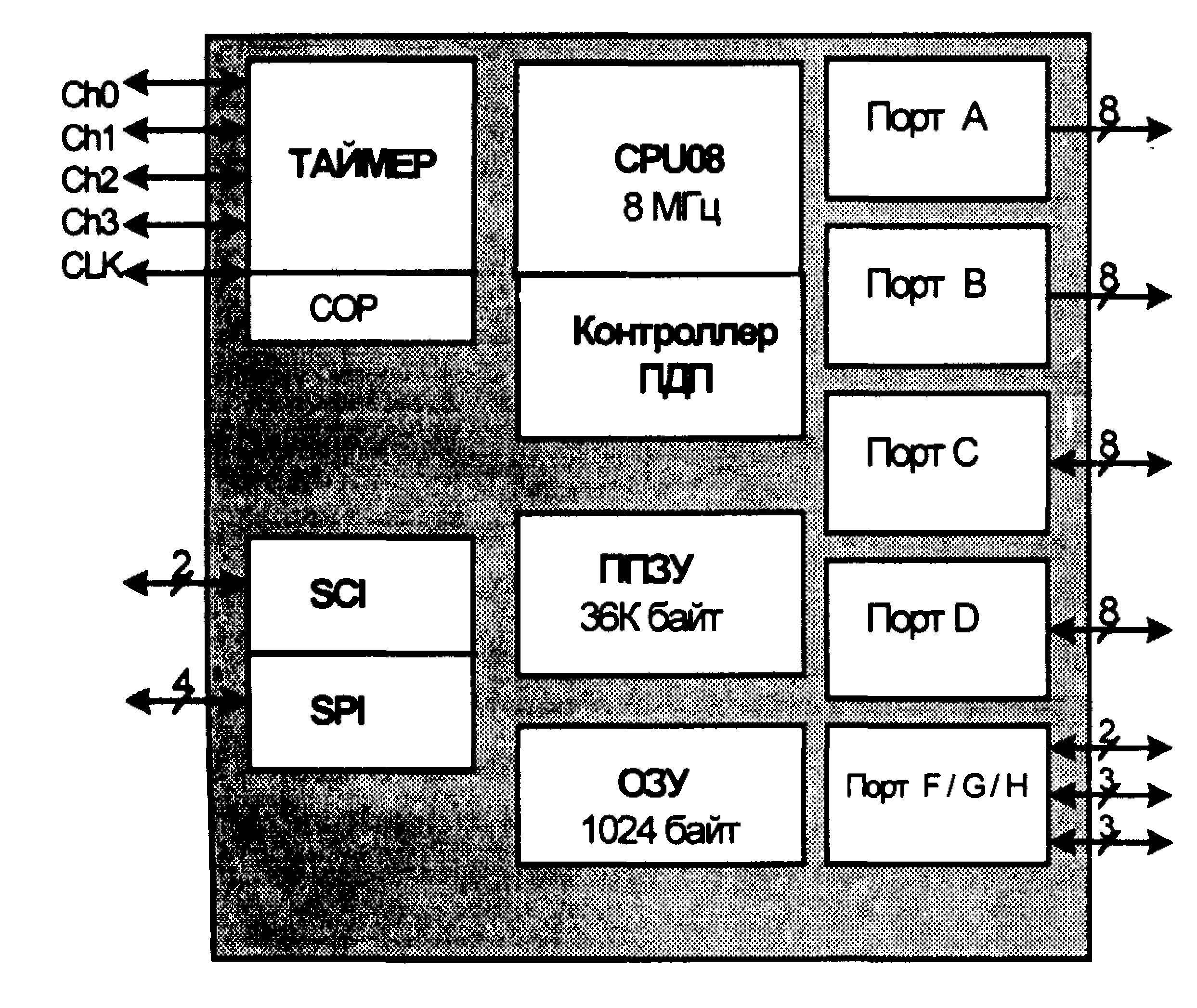

Примером структуры МК семейства РС08 может служить МК МС68НС708XL36, который изображен на рис.1.5.

Его составляющие:

высокопроизводительный модуль CPU08 с тактовой частотой 8 МГц,

36 Кбайт ППЗУ,

1К статического ОЗУ,

16-разрядный 4-канальный таймер,

последовательные интерфейсы CI и SPI,

3-канальный контроллер ПДП,

сторожевой таймер,

систему обнаружения пониженного напряжения, неправильного кода и адресов,

40 двунаправленных линий ввода-вывода.

<

>

Рис.1.5. Структурная схема МК МС68НС708XL36

1.1.3. Семейство НС11

Семейство НС11 в отличие от МК "заказных" семейств, содержит около 40 универсальных МК, ориентированных как массовое производство, так и на мелкое и среднее производство.

Все МК содержат одинаковое 8-разрядное ЦПУ "второго поколения" (МС6809), которое отличается повышенной производительностью, эффективной системой команд и методами адресации. МК семейства НС11 содержат встроенную память различных типов и конфигураций. Периферийные устройства представлены подсистемами, наиболее часто требующимися во встроенных системах: таймеры, АЦП, ШИМ, ЦАП, последовательный интерфейс и встроенный сопроцессор.

ЦПУ семейства удобно для программирования. Его особенности (рис.1.6):

2 8-битных или 1 16-битный аккумулятор,

2 16-битных индексных регистра,

2 программно управляемых режима пониженного энергопотребления,

операции умножения 8х8 и деления 16/16,

внутренняя тактовая частота до 4 МГц.

<

Рис. 1.6. Структурная схема ЦПЭ семейства НС11

Система команд состоит из следующих групп:

команды пересылки данных через аккумуляторы,

команды пересылки для стека и индексных регистров,

команды переходов и работы с подпрограммами,

арифметические команды,

команды работы с битами,

специальные команды.

Встроенная память МК имеет в своем составе все типы памяти, которые доступны для НС05. Все МК адресуют внешнюю память, есть версии с немультиплексированными шинами данных и адреса, а также с расширенным до 256 К...1Мбайт адресным пространством.

МК функционируют в одном из трех режимов, которые задаются с помощью специальных входов при сбросе:

однокристальный режим - программа находится во внутреннем ППЗУ, при этом порты доступны для ввода-вывода,

расширенный режим - возможно подключение памяти программ или данных

режим загрузки - управление после сброса передается в масочное ПЗУ, в котором находится программа загрузки кода с ПЭВМ по последовательному каналу в любую часть памяти (даже в ППЗУ и EEPROM).

МК этого семейства позволяют программно переназначать начало областей ОЗУ, ППЗУ и регистров в любую область с кратностью 4 К.

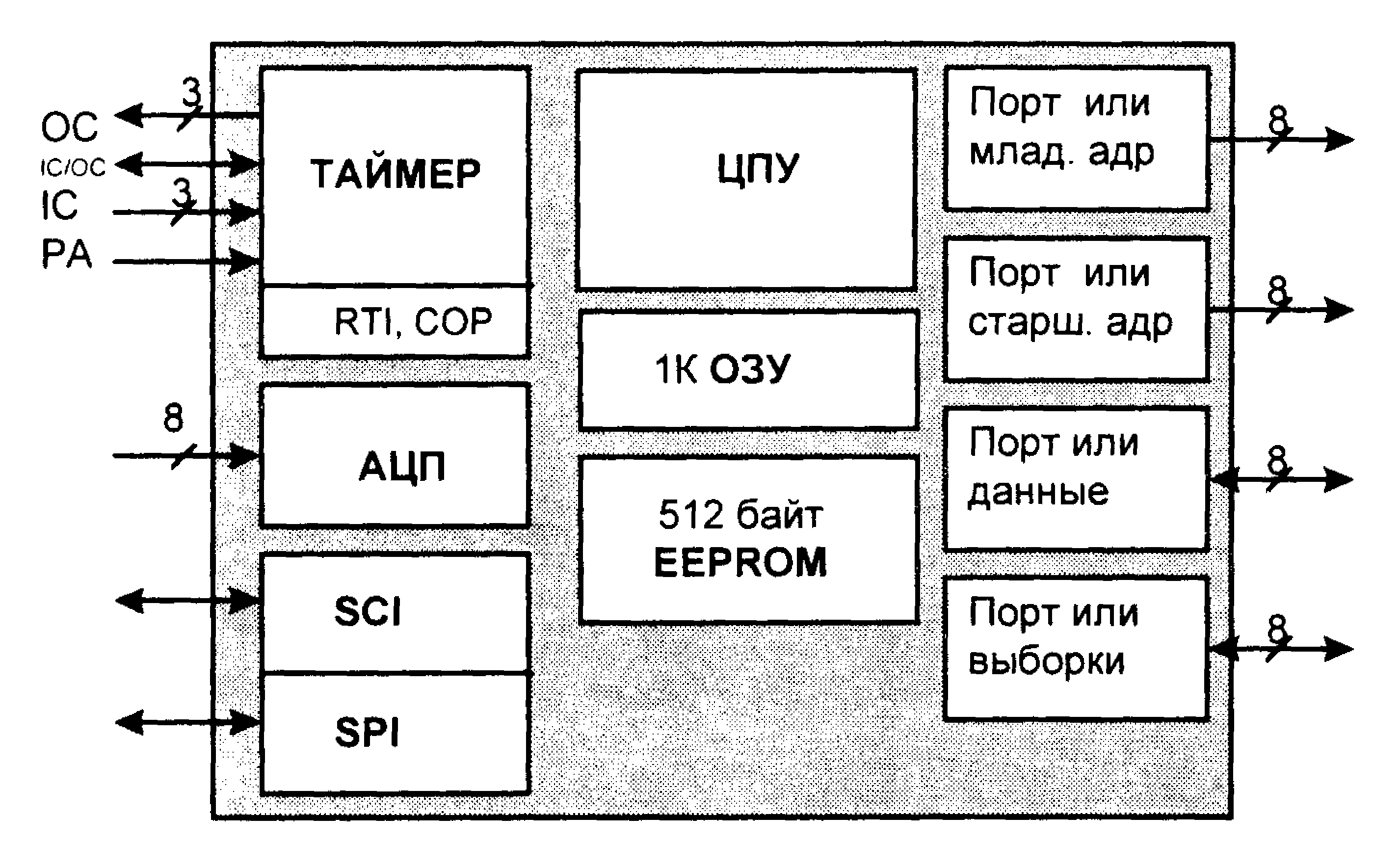

Примером МК семейства НС11 может служить МК MC68HC11F1, предназначенный Рис. 1.7. Структурная схема МК MC68HC11F1

для работы в средствах связи, промышленного упрапвления. У него нет встроенного ППЗУ.

Основные характеристики МК:

немультиплексированная шина адреса-данных, частота 4 МГц,

4 программируемой выборки для внешней памяти или внешних устройств,

512 байт EEPROM, 1024 байт ОЗУ,

16-разрядный таймер: 3-4 канала входной фиксации, 4-5 выходных каналов со сравнением,

АЦП 8-р 8 каналов,

2 последовательных интерфейсов: асинхронный и синхронный.

<

>

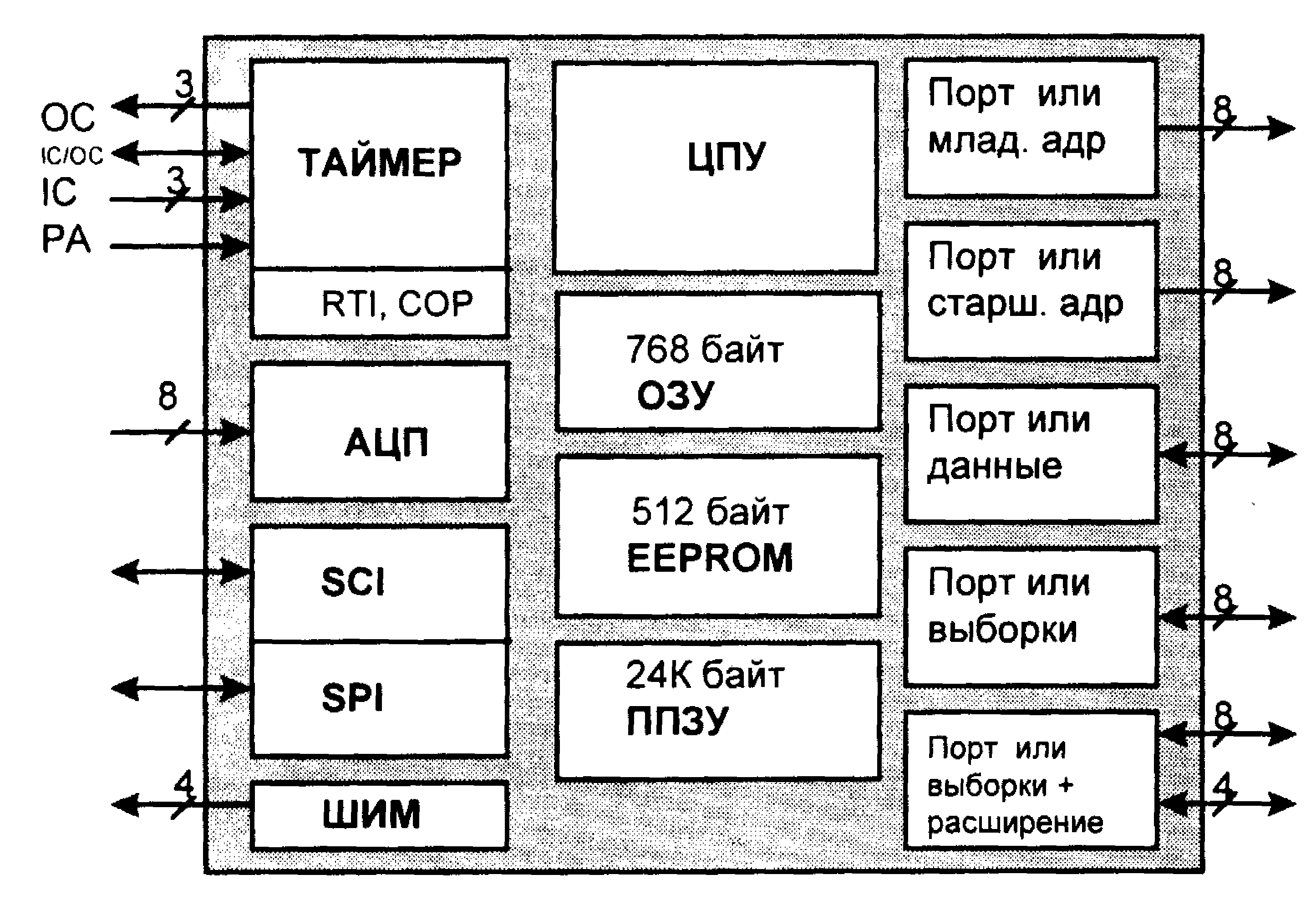

Другим примером применения МК, где требуется большой объем встроенной памяти, служит использование МК МС68НС711К4. Он имеет:

немультиплексированная шина адреса-данных, частота 4 МГц,

768 байт ОЗУ, 640 байт EEPROM,

24 Кбайт ППЗУ,

16-разрядный таймер,

4-канальный 8-разрядный ШИМ,

последовательные интерфейсы SCI+SPI,

возможность адресации внешней памяти объемом до 1 Мбайт.

<

Рис. 1.8. Структурная схема МК МС68НС711К4

1.1.4. 16- и 32-разрядные микроконтроллеры MOTOROLA

Высокопроизводительные 16- и 32-разрядные микроконтроллеры семейств Motorola 68НС16, 68300 реализуются из набора стандартных функциональных модулей. Набор модулей содержит 16- или 32-разрядный процессор (CPU16 или CPU32), модули внутренней памяти, модуль системной интеграции (SIM или SCIM), модуль последовательного интерфейса (QSM), таймерный процессор (TPU) или таймерный модуль (GPT), аналого-цифровой преобразователь (ADC) и ряд других. Размещенные на кристалле модули соединяются стандартной межмодульной шиной. Микроконтроллеры семейства 68НС16 содержат 16-разрядный процессор CPU 16, который является дальнейшим развитием 8-разрядного процессора, используемого в семействе 68НС11. Микроконтроллеры семейства 68300 содержат процессоры CPU32, функционально аналогичные микропроцессорам MC68020.

Коммуникационные контроллеры, которые входят в состав семейства 68300, предназначены для использования в системах связи. Они содержат модуль коммуникационного RISC-процессора и имеют расширенный состав модулей обмена данными. В качестве процессорного ядра они используют различные модификации микропроцессоров семейства Motorola 68000.

1.1.5. Номенклатура и области применения микроконтроллеров семейства 68НС16

Архитектура семейства 68НС16 является дальнейшим развитием архитектуры 8-разрядных семейств 68НС05,08,11. Реализуемое в микроконтроллерах 68НС16 увеличение объема адресуемой памяти до 1 Мбайт, повышение тактовой частоты до 16 МГц, обработка 16- и 32-разрядных чисел, введение команд умножения-накопления (MAC) дробных чисел и ряд других характеристик позволяют значительно повысить производительность и расширить функциональные возможности систем, реализуемых на их основе. Поэтому микроконтроллеры данного семейства используются в тех случаях, когда необходимо существенно модернизировать схему управления каким-либо устройством, реализованную на базе семейств 68НС05,11, не меняя кардинально ее структуру и принципы функционирования. Эти микроконтроллеры широко применяются в качестве центральных блоков управления в системах, которые содержат несколько микроконтроллеров 68НС05,11, обслуживающих отдельные объекты.

Таблица 1.1

Модель |

ПЗУ бит |

ОЗУ бит |

ЭСППЗУ бит |

Таймер |

Входы-выходы |

Послед. порт |

АЦП |

Модуль

интеграции |

MC68HC16Z1 |

1 К |

GPT |

46 |

QSM |

10р.,8вх |

SIM |

||

MC68HC16Z2 |

8К |

2К |

— |

GPT |

46 |

QSM |

10р.,8вх |

SIM |

MC68HC16Z3 |

8К |

4К |

— |

GPT |

46 |

QSM |

10р.,8вх |

SIM |

MC68HC16Y1 |

48К |

1К |

— |

TPU+GPT |

95 |

SPI+2SCI |

10р.,8вх |

SCIM |

MC68HC16S1 |

— |

2К |

— |

— |

23 |

— |

— |

— |

MC68HC16V1 |

— |

— |

— |

GPT |

62 |

QSPM+SCI |

— |

- |

MC68HC916Y1 |

4К |

48 К |

TPU+GPT |

95 |

SPI+2SCI |

10р.,8вх |

SCIM |

|

МС68НС916Х1 |

— |

2К |

50 |

GPT |

95 |

SPI+2SCI |

10р.,8вх |

SCIM |

Использование микроконтроллеров 68НС16 обеспечивает также значительное улучшение характеристик систем, выполняющих цифровую обработку поступающих сигналов, которая производится с помощью специальных регистров и команд MAC процессора CPU 16. Реализуемый в этих микроконтроллерах режим отладки BDM существенно упрощает процедуру отладки систем, построенных на их основе.

Микроконтроллеры семейства 68НС16 используются в системах управления автомобильным оборудованием, телекоммуникационной аппаратуре (сотовые телефоны, телефонные коммутаторы), бытовой электронике (видеокамерах, телевизорах, цифровых аудиосистемах), офисной технике (факсы, модемы, копировальная техника), медицинском оборудовании, робототехнике.

1.1.6. Номенклатура и области применения микроконтроллеров семейства 68300

В архитектуре микроконтроллеров 68300 использованы принципы, заложенные в микропроцессорном семействе 68000. Применение 32-разрядного процессора CPU32, имеющего широкий набор команд и способов адресации, расширение адресуемой памяти до 16 Мбайт и ряд других особенностей делают микроконтроллеры семейства 68300 эффективным средством для реализации сложнофункциональных и высокопроизводительных систем, которые могут использовать огромный объем программного обеспечения, разработанного для микропроцессоров семейства 68000, включая ассемблеры, компиляторы, отладчики, операционные системы, а также многочисленные прикладные программы. Все это делает семейство 68300 перспективной элементной базой для реализации новых поколений систем управления.

Микроконтроллеры семейства 68300 имеют напряжение питания 5 В, максимальную тактовую частоту 20 МГц и потребляемую мощность в рабочем режиме не более 600 мВт, которая снижается в режиме останова до 500 мкВт. Предусмотрено подключение к памяти пониженного резервного питания, что позволяет сохранить ее содержимое в режиме хранения. Все модели микроконтроллеров содержат сторожевое устройство (WDT-watchdog timer), таймер для реализации периодических прерываний (PIT), а также реализуют режим отладки BDM.

Микроконтроллер МС68331 является наиболее простой моделью семейства 68300. Он не имеет внутренней памяти и модуля АЦП, использует более простой таймерный модуль GPT. Основное применение находит в системах регулирования и контрольно-измерительной аппаратуре. Микроконтроллер МС68332 послужил базовой моделью, на основе которой реализован ряд последующих моделей. Получил широкое распространение в робототехнике, автомобильной электронике, устройствах управления электродвигателями, системах промышленной автоматики.

Таблица 1.2

Модель |

ОЗУ

Кбайт |

ЭСППЗУ Кбайт |

Таймер |

ОЗУ

таймера |

Входы-выходы |

Послед. порт |

АЦП |

Модуль интеграции |

МС68331 |

— |

— |

GPT |

— |

43 |

QSM |

— |

SIM |

МС68332 |

2 |

— |

TPU |

— |

47 |

QSM |

— |

SIM |

МС68333 |

0,5 |

64 |

три |

3,5 К |

96 |

QSM |

10р.,8вх |

SCIM |

МС68334 |

— |

— |

TPU |

1К |

47 |

- |

10р.,8вх |

SCIM |

МС68335 |

8 |

— |

TPU |

2К |

47 |

QSM |

— |

SIM |

МС68336 |

4 |

— |

TPU+CTM |

3,5 К |

96 |

QSM |

10р.,8вх |

SIM |

МС68376 |

4 |

— |

TPU+CTM |

3,5 К |

96 |

QSM+CAN |

10р.,8вх |

SIM |

Микроконтроллер МС68333 является функциональным расширением модели МС68332, в которую введены электрически стираемое ППЗУ (Flash) емкостью 64 Кбайт, 10-разрядный АЦП с 8 аналоговыми входами, ОЗУ таймерного процессора емкостью 3,5 Кбайт. Разработанный первоначально для систем управления автомобильными двигателями, этот микроконтроллер в настоящее время находит также широкое применение в промышленной автоматике и связной аппаратуре. Микроконтроллер МС68334 является упрощенным вариантом МС68333, в котором исключены ЭСППЗУ, ОЗУ и модуль последовательного обмена QSM. Благодаря этому значительно снижена его стоимость, что весьма существенно для многих применений. Используется, главным образом, во встраиваемых системах управления.

Микроконтроллеры МС68336, 376 обладают наиболее широкими функциональными возможностями. Кроме TPU они содержат модуль конфигурируемого таймера СТМ, имеющего четыре канала, которые программируются на выполнение различных функций. Для аналого-цифрового преобразования используется модуль QADC, который отличается от ADC введением буфера (очереди) данных. В модели МС68376 дополнительно введен модуль сетевого контроллера, реализующего промышленный протокол CAN. Эти микроконтроллеры служат для решения задач высокоточного регулирования и сложнофункционального управления.

В состав семейства 68300 входят также ряд моделей, которые содержат типовые модули, используемые в микропроцессорных системах, или специализированные модули для специфических областей применения. Такие модели называются интегрированными микропроцессорами (МС68306, 307, 328, 330, 340, 341, 349) и специализированными контроллерами (МС68322 - контроллер формирования изображений, МС68302, 356, 360 - коммуникационные контроллеры).

Интегрированные микропроцессоры используют в качестве процессорного ядра различные варианты CPU32. Модуль CPU030 содержит процессор CPU32+, обеспечивающий работу с 32-разрядными адресами и данными, и два модуля памяти: ОЗУ данных и конфигурируемый кэш команд. ОЗУ данных состоит из четырех блоков емкостью по 1 Кбайту, размещаемых в любом месте адресного пространства. Конфигурируемый кэш команд состоит из четырех блоков, каждый из которых может работать как кэш-память емкостью 256 байт или ОЗУ емкостью 512 байт. Таким образом, можно реализовать кэш команд емкостью до 1 Кбайта или ОЗУ емкостью до 2 Кбайт. Процессор 68ЕСООО представляет собой процессорное ядро микропроцессора МС68ЕСООО, который функционально аналогичен MC68000.

Таблица 1.3

Модель |

Процессор |

ОЗУ

бит |

Таймеры |

Послед. порт |

Модуль интеграции |

Дополнительные модули |

МС68306 |

68ЕС000 |

- |

DUART |

SIM |

Контроллер ДОЗУ |

|

МС68307 |

68ЕС00 |

- |

2ТС |

DUART |

MSB |

Контроллер шины M-bus (I2C) |

МС68322 |

68ЕС000 |

SIM |

Видеоконтроллер, графический процессор контроллер ПДП-2кан., контроллер ДОЗУ |

|||

МС68328 |

68ЕС00 |

- |

2ТС |

UART |

SIM40 |

Контроллер ЖКИ, ТРВ |

МС68330 |

CPU32 |

- |

- |

- |

SIM40 |

Контроллер PCMCIA |

МС68340 |

CPU32 |

- |

2ТС |

DUART |

SIM40 |

Контроллер ПДП-2кан. |

МС68341 |

CPU32 ^ |

- |

2ТС |

DUART, SPI DUART |

SIM41 |

Контроллер ПДП-2кан., ТРВ |

МС68349 |

CPU030 |

4К+2К |

2ТС |

SIM49 |

Контроллер ПДП-2кан., ТРВ |

Большинство интегрированных микропроцессоров содержит два 16-разрядных таймера-счетчика, которые могут переключаться как тактовыми импульсами, так и внешними сигналами. Для последовательного обмена чаще всего применяются сдвоенные (DUART) или одиночные (UART) асинхронные приемо-передатчики (аналогичны микросхеме МС68681). В состав ряда моделей входят синхронные последовательные порты SPI или специальные синхронные порты SSI. В качестве модуля системной интеграции используются различные модификации SIM. Модуль интеграции MSB в модели МС68307 обеспечивает интерфейс с шинами семейств 68000, 8051 и M-bus, реализующей промышленный протокол обмена I2C.

Для интегрированных микропроцессоров и специализированных контроллеров характерно широкое использование таких дополнительных модулей, как контроллеры динамических ОЗУ, обеспечивающие периодическую регенерацию хранящейся в них информации, контроллеры прямого доступа к памяти (ПДП), обслуживающие обычно 2 канала обмена. Некоторые контроллеры содержат дополнительные RISC-процессоры, ориентированные на выполнение определенных функций. В модели МС68322 это графический процессор RGP, работающий совместно с контроллером принтера PVC. В моделях МС68302, 356, 360 это коммуникационные процессоры СР или СРМ, обеспечивающие управление сетями передачи информации с разными протоколами обмена. Контроллер МС68356 содержит в качестве дополнительного модуля 24-разрядный цифровой процессор сигналов (DSP) с памятью емкостью 10Кх24 бит, который аналогичен DSP5602, выпускаемому компанией МОТОРОЛА в качестве отдельного изделия. Модели МС68330, 356 имеют также контроллер интерфейса с широко используемой шиной PCMCIA. Модель 68328 содержит контроллер широкоформатного жидкокристаллического дисплея высокого разрешения.

Данные микропроцессоры функционируют с максимальной тактовой частотой 16,20 или 25 МГц (для различных модификаций). Модели МС68307, 328, 330, 340, 341, 349 имеют модификации, работающие при пониженном напряжении питания 3,3 В, которые используются в портативной аппаратуре.

Основной областью применения интегрированных микропроцессоров МС68306, 307, 322, 328 являются вычислительные и управляющие устройства, встраиваемые в различную аппаратуру. Там же находят применение и микропроцессоры МС68330, которые имеют более мощный процессор, но содержат ограниченный набор дополнительных блоков. Данная модель отличается более низкой стоимостью. Модель МС68340 имеет достаточно широкий набор дополнительных модулей и используется в устройствах, требующих быстрой передачи и обработки больших массивов данных, например, в контроллерах дисковых накопителей. Модель МС68341 разработана для управления накопителями на компакт-дисках (CD-ROM). Модель МС68349, имеющая наиболее широкие функциональные возможности, предназначена для реализации компактных и высокопроизводительных систем управления и обработки данных, встраиваемых в связную, контрольно-измерительную, медицинскую и другую аппаратуру. Контроллер МС68322 используется, главным образом, в лазерных принтерах и других высокопроизводительных печатающих устройствах. Контроллер МС68328 ориентирован на применение в сложнофункциональной портативной аппаратуре с широкоформатными жидкокристаллическими дисплеями.

Коммуникационные контроллеры МС68302, 356, 360 предназначены для использования в системах обмена информацией. Специфические особенности их функционирования и применения связаны с наличием коммуникационного процессора СРМ, обеспечивающего возможность подключения к линиям связи с различными протоколами обмена. В состав СРМ входят RISC-контроллер, двухпортовое ОЗУ и большой набор периферийных устройств, который включает:

- четыре связных последовательных контроллера SCC1 - SCC4;

- два управляющих последовательных контроллера SMC 1, SMC2;

- периферийный последовательный интерфейс SPI;

- блок последовательного обмена с временным разделением данных;

- параллельный порт, реализующий стандартный протокол обмена типа CENTRONICS;

- три параллельных порта, обеспечивающих различные протоколы квитированного и неквитированного обмена;

- четыре 16-разрядных таймера (могут конфигурироваться как два 32-разрядных);

- двухканальный блок независимого прямого доступа к памяти.

Кроме того можно дополнительно реализовать шестнадцать 16-разрядных таймеров и четырнадцать каналов

последовательного прямого доступа к памяти.

Модули СРМ в моделях МС68360 и MC68EN360, МС68МН360 имеют одинаковые структуры и режимы функционирования. Различие между ними состоит только в наборе протоколов обмена, реализуемых интерфейсами SCC. В MC68EN360 интерфейсы SCC могут обеспечивать протокол обмена по локальной сети Ethernet. В МС68МН360 реализуется протокол HDLC с многоканальным обменом, а для SCC1 также протокол сети Ethernet

Наиболее сложные протоколы последовательной пересылки реализуют связные контроллеры SCC 1-4, каждый из которых программируется путем загрузки соответствующего содержимого в регистр режима. В зависимости от этого SCC обеспечивает один из следующих протоколов обмена: HDLC/SDLC, UART, AppleTalk, BYSINC или транспарентный обмен.

Таблица 1.4

Тип контроллера |

68360 |

68EN360 |

68МН360 |

CPU SIM |

CPU32+ SIM60 |

CPU32+ SIM60 |

CPU32+ SIM60 |

SCC SMC SPI |

4 2 1 |

4 2 1 |

4 2 1 |

Каналы ПДП |

2+14 |

2+14 |

2+14 |

Таймеры |

4+16,PIT,WDT |

4+16,PIT,WDT |

4+16,PIT,WDT |

Ethernet |

— |

4 |

1 |

Отладка |

JTAG, BDM |

JTAG, BDM |

JTAG, BDM |

Дополнительные возможности |

CENTRONICS, КДП*) |

CENTRONICS, КДП*) |

32*HDLC, КДП*) |

1.2. Производители микроконтроллеров семейства MCS51

Существенным фактором н выборе вычислительного ядра были и остаются цена, доступность и время поставки.

Фирма Intel являемся законодателем и основоположником архитектуры семейства MCS51. Фирма выпускает более 50 различных вариантов микроконтроллеров. Из них 11 в виде специализированных устройств. Предлагается изготовление кристаллов на заказ. В настоящий момент она сворачивает выпуск изделии семейства MCS51 и предлагает использовать процессоры нового семейства с улучшенными скоростными характеристиками и чертами 16-разрядных процессоров

Фирма Dallas Semiconductor выпускает микроконтроллеры с улучшенной архитектурой. Можно выделить два основных направления. Bo-первых, изменены принципы размещения программ внутри кристалла и создан контроллер, способный и самостоятельно модифицировать часть своих программ. Во-вторых, фирма утроила быстродействие за счет изменения временных характеристик с одновременным введением средств сбережения энергии. Приборы этой фирмы предназначены для применения в скоростных, переносных, экономичных и труднодоступных для обслуживания устройствах.

Фирма Siemens Components Inc выпускает удобные для использования в бытовой, в том числе и видео технике, микроконтроллеры. Микросхемы содержат разнообразные встроенные устройства (АЦП, массивы счетчиков, дополнительный блок умножения и деления, расширение портов ввода-вывода).

Фирма Philips Semiconductors разрабатывает микроконтроллеры семейства 8051 на базе американской компании Signetics. Процессоры этой фирмы ориентированы на работу в бытовой или автомобильной технике. Благодаря аппаратной реализации шин I2С и CAN, легко могут быть использованы в инструментальных комплексах. Микросхемы содержат разнообразные встроенные устройства (АЦП, массивы счетчиков, расширение портов ввода-вывода), Имеются варианты с пониженным питающим напряжением и в компактных корпусах.

Фирма OKI Semiconductor выпускает полностью статические микросхемы по технологии CMOS, являющиеся функциональными аналогам микросхем фирмы Intel с дополнительными возможностями. Имеют улучшенные характеристики по цепям питания. Впервые применила корпус PIGGYBACK, в котором внутренняя шина вынесена наружу в виде разъема для установки ПЗУ

Фирма Matra MHS выпускает статические микросхемы, являющиеся аналогами стандартных моделей семейства MCS51 с улучшенными выходными цепями портов ввода-вывода.

Фирма Advanced Micro Devices (AMD) выпускает микросхемы по технологиям CMOS и NMOS, являющиеся функциональными аналогами микросхем фирмы Intel с дополнительными возможностями.

Фирма Fujitsu. Фирма выпускает функциональные аналоги микросхем 80С31, 8051 87С51 фирмы Intel по технологии NMOS.

Объединение Atmel выпускает стандартные микроконтроллеры с ПЗУ по технологии Flash и объемом до 20 Кбайт в обычных и уменьшенных корпусах. В последнее время фирма начала выпуск принципиально новых МК, основанных на RISC архитектуре.

Таким образом, на рынке МК семейства MCS51 можно выделить 3 направления: "традиционное" - но с улучшенными характеристиками памяти и внешних устройств, "быстродействующее" - обеспечивающее увеличение скорости выполнения операций, и "специальное" - с коренным изменением процесса обработки информации. Первое направление поддерживается МК фирм Atmel, Philips и другими. Второе - МК фирмы Dallas Semiconductor, а третье - новыми МК фирм Atmel и Dallas Semiconductor. Рассмотрим более подробно некоторые семейства МК этих трех направлений.

1.3. 8-разрядные КМОП FLASH микроконтроллеры семейства АТ89.

1.3.1. Отличительные особенности

• 8-разрядное ЦПУ, оптимизированное для функций управления

• расширенные возможности побитовой обработки

• встроенная flash память программ

• встроенное ОЗУ данных

• пвунаправленные индивидуально адресуемые линии ввода/вывода

• встроенные 16-разрядные таймеры/счетчики событий

• полный дуплексный UART

• несколько источников прерываний с несколькими уровнями приоритета

• встроенный тактовый генератор

• встроенное ЭСППЗУ (серия AT89S)

• интерфейс последовательной шины SPI (серия AT89S)

• сторожевой таймер (серия AT89S)

• пассивный (idle) и стоповый (power doun) режимы

• возможность расширения внешнего ОЗУ и ПЗУ до 64 Кбайт

• режим внутрисхемной эмуляции (ONCE™ - on circuit emulation)

КМОП микроконтроллеры семейства АТ89 оснащены Flash программируемым и стираемым ПЗУ, совместимы по системе команд и по выводам со стандартными приборами семейства MCS-51™ Микроконтроллеры содержат Flash ПЗУ емкостью от 1 Кбайта до 8 Кбайт, ОЗУ,емкостью от 64 байтов до 256 байт, большое количество программируемых линий ввода/вывода, 16-разрядные таймеры/счетчики событий, полнодуплексный последовательный порт (UART), набор векторных прерываний с несколькими уровнями приоритета, встроенные генератор и схему формирования тактовой последовательности. Программирование микроконтроллеров семейства АТ89 возможно, в зависимости от типа, внутрисистемно, с использованием при программировании напряжения питания системы, и с использованием программаторов. Содержимое Flash памяти программ может быть защищено от несанкционированной записи/считывания. У ряда микроконтроллеров имеется возможность очистки Fiash памяти за одну операцию, возможность считывания встроенного кода идентификации.

В активном режиме микроконтроллеры на частоте 12 МГц потребляют порядка 25 мА и в пассивном режиме, при котором остановлено ЦПУ, но система прерываний, ОЗУ, таймеры/счетчики событий и последовательный порт остаются активными, потребление снижается до 15% от потребления в активном режиме. В стоповом режиме потребление не превышает 100 мкА. Микроконтроллеры семейства АТ89 ориентированы на использование в качестве встроенных управляющих контроллеров в промышленном (-40 °С...+85°С) и коммерческом (0°C...70°C) диапазонах температур. Имеются исполнения микроконтроллеров АТ89С51 и АТ89С52, соответствующие требованиям, предъявляемым к приборам используемым в автомобильном (-40°С ...125°С), Military и Military-883C (-55 °C...+125°C) диапазонах температур.

Таблица 1.5

Основные характеристики микроконтроллеров семейства АТ89

Наименование прибора |

Совместимость |

Напряж.

VCC, В |

Объем

ПЗУ ЭСППЗУ, байт |

Объем

ОЗУ, байт |

Группы по тактовой частоте, МГц |

Потребление макс. в активн. (пасс.) режиме, f=12 МГц, VCC=6B, мА |

АТ89С1051 |

80С31 |

2,7...6 |

1 К |

64 |

12,24 |

15(5) |

АТ89С2051 |

80С31 |

2.7...6 |

2 К |

128 |

12,24 |

15 (5) |

АТ89С51 |

80С31 |

5±20% (5±10%) |

4К |

128 |

12,16, 20/24 |

20(5) |

AT89LV51 |

80С31 |

2,7...6 |

4К |

128 |

12 |

20(5) |

АТ89С52 |

80С32 |

5±20% (5±10%) |

8К |

256 |

12,16, 20,24 |

25 16/51 |

AT89LV52 |

80С32 |

2,7...6 |

8К |

256 |

12 |

25 (6,5} |

AT89S8252 |

80С32 |

2,7±10% |

8 К |

256 |

12(2,7 В),

24(5 В) |

1.4. Высокопроизводительные 8-разрадные RISC контроллеры семейства AT90S

1.4.1. Вычислительные особенности

Производительность, приближающаяся к 1 MIPS/МГц

Усовершенствованная AVR RISC архитектура

Раздельные шины памяти команд и данных, 32 регистра общего назначения

Flash ПЗУ программ с возможностью внутрисистемного перепрограммирования и загрузки через SPI последовательный канал, 1000 циклов стирание/запись

ЭСППЗУ данных/ с возможностью внутрисистемной загрузки через SPI

Последовательный канал/ 100000 циклов стирание/запись

Блокировка режима программирования

Встроенные аналоговый компаратор/ сторожевой таймер, порты SPI и UART/ таймеры/

Полностью статические приборы - работают при тактовой частоте от 0 Гц до 20 МГц

Диапазон напряжений питания от 2,7 В до 6,0 В

Режимы энергосбережения: пассивный (idle) и стоповый (power down)

КМОП микроконтроллеры семейства AT90S выполнены по AVR™ RISC архитектуре с раздельной памятью программ и данных и раздельными шинами для памяти программ и данных (Гарвардская архитектура). AVR ядро объединяет мощную систему команд с 32 регистрами общего назначения и конвейером (в одном цикле одна команда выполняется а другая выбирается) выборки из памяти программ. Все 32 регистра напрямую связаны с АЛУ, что позволяет выполнять обращение к двум независимым регистрам и возвращать результат одной командой, выполняемой в одном цикле. Шесть регистров могут использоваться как три 16-разрядных указателя адреса данных (кроме прибора AT90S1200). Выполняя команды за один тактовый цикл, прибор обеспечивает производительность, приближающуюся к 1 MIPS на МГц, что на порядок больше, чем у CISC микроконтроллеров. Архитектура эффективно поддерживает как языки высокого уровня, так и программы, написанные на экстремально плотных языках ассемблера.

Микроконтроллеры семейства оснащены встроенной загружаемой Flash памятью EEPROM, обеспечивающей внутрисистемное перепрограммирование с использованием интерфейса SPI или программирование внешними стандартными программаторами энергонезависимой памяти. Поскольку все команды 16-разрядного или 32-разрядного формата, то Flash память программ имеет 16-разрядную организацию. В качестве памяти данных в микроконтроллерах семейства используется комбинация СОЗУ и ЭСППЗУ (у прибора AT90S1200 только ЭСППЗУ) в которых размещается также и пространство памяти ввода/вывода. Стек, предназначенный для хранения адресов возврата из подпрограмм и прерываний располагается в памяти данных (у прибора AT90S1200 стек выполнен аппаратно). Ряд AVR микроконтроллеров имеют встроенный в арифметическую часть АЛУ перемножитель.

Таблица 1.6

Основные характеристики микроконтроллеров семейства AT90S.

Тип прибора |

Объем памяти (организация), бит |

Объем (СОЗУ) памяти данных, байт |

Тактовая частота, МГц. |

Таймеры/счктчики, кол-во х разрядность |

Другие отличия |

Потребл. в активном/пассивном Vсс=ЗВ, f=4 МГц, мА |

AT90S1200 |

1 К (512x16) |

64x8 |

0...12 |

1x8 |

15 линий I/O, аппаратный стек |

2/0,5 |

A9OS2313 |

2 К (1Кх16) |

128х8 |

0...10 |

1х8,

1х16 |

15 линий I/O, ШИМ, UART |

2,5/0,8 |

AT90S2323 |

2 К

(lKx16) |

128х8 (128х8) |

0...10 |

1х8 |

3 линии I/O, |

3/1,2 |

АТ90S2343 |

2 К

(lKx16) |

128х8 (128х8) |

0...10 |

1х8 |

5 линий I/O, |

3/1,2 |

A90S4414 |

4К

(2Кх16) |

256х8

(256х8) |

0...8 |

1х8,

1х16 |

32 линии I/O, ШИМ, UART |

3,5/1 |

AT90S4434 |

4К

(2Кх16) |

256х8 (256х8) |

0...8 |

2х8, 1х16 |

32 линии I/O, ШИМ, UART 8xl0 АЦП, аналог. компаратор |

3/1,2 |

AT90S8535 |

8K (4Кх16) |

512х8

(512x8) |

0...8 |

2х8, 1х16 |

32 линии I/O, ШИМ, UART 8xl0 АЦП, аналог. компаратор |

3/1,2 |

АТ9058515 |

8K (4Кх16) |

256х8

(256х8) |

0...8 |

1х8,1х16 |

32 линии I/O, ШИМ, UART |

3,5/1.2 |

ATmega103 |

128 К

(64Кк16) |

4Кх8 (4Kx8) |

0...6 |

3х16 |

40 линий I/O, 3 ШИМ, UARТ, 8xl0 АЦП, аналог. компаратор |

3/1,2 |

AТmega603 |

64 К

(32Kx16) |

2Кх8

(4Кх8) |

0...6 |

3х16 |

40 линий I/O, 3 ШИМ, UARТ, 8xl0 АЦП, аналог. компаратор |

3.0/1,2 |

Микроконтроллеры семейства AT90S поставляются в очищенном состоянии - содержимое и Flash памяти программ и ЭСППЗУ данных находится в состоянии FF и готово к программированию.

Объединение на одном кристалле усовершенствованного 8-разрядного RISC ЦПУ с загружаемым Flash ПЗУ позволило фирме создать мощные микроконтроллеры, обеспечивающие высокую гибкость и экономичность в использовании приборов в качестве встраиваемых контроллеров.

1.5. Программируемые контроллеры фирмы Dallas Semiconductor

1.5.1. Микроконтроллеры с динамической организацией (Soft Мicго)

Номенклатура микроконтроллеров с динамической организацией состоит из базовых микропроцессоров, объединенных с БИС памяти, с определенными принципами организации памяти. Дополнительно часто используются устройства, имеющие небольшие размеры и которые могут быть использованы как прямые функциональные части стандартных микроконтроллеров MCS51. Перечень изделий этого семейства, быстродействие и объем памяти указаны в табл. 1.7.

Все базовые микропроцессоры не имеют собственной встроенной памяти и при их использовании необходимо (на дополнительную шину и без привлечения портов ввода-вывода) установить нужный кристалл малопотребляющей памяти, а к специальному выводу присоединить литиевую батарею на 3 вольта. При правильном выборе типа памяти энергии литиевой батареи хватает для хранения информации не менее 12 лет. Эта энергия расходуется только при отключенном питании 5 вольт, когда процессор находится в нерабочем состоянии. Все базовые кристаллы размещены в корпусах QFP80 с выводами по поверхностный монтаж и расстоянием 08 мм между выводами.

Изделия выполнены в корпусах DIP40 или SIP STICK и представляют микромодули с установленными базовым контроллером, памятью, таймером реального времени и литиевой батарейкой. Работа таймера и сохранение содержимого памяти при отсутствии "питающего" напряжения обеспечивается энергией литиевой батарейки, Выводы изделий в DIP40 совпадают с выводами микроконтроллеров MCS51 и аналогичных корпусах, что позволяет осуществлять их замену. Печатные платы SIP STICK предназначены для установки в разъемы SIMM40 или SIMM 72 (выпускаются только этой фирмой). Использование SIP STICK позволяет экономить площадь монтажной платы, за счет вертикального расположения модулей. При одинаковых характеристиках, самым дешевым является создание собственных изделий с использованием базовых кристаллов, самым дорогим применение модулей в DIP40. Модули SIP STICK занимают промежуточное положение.

Таблица 1.7

Название |

Тактовая частота |

Объем памяти |

: Особенности |

Базовые микропроцессоры |

|||

DS5000FP |

до 8, 12 или 16 МГц |

до 64 Кбайт |

Кодировка памяти |

DS5001FP |

до 12 или 16 МГц |

до 128 Кбайт |

|

DS5002FP |

до 12 или 16 МГц |

до 128 Кбайт |

Кодировка памяти |

Изделия на базе DS5000FP |

|||

DS5000 |

до 8, 12 или 16 МГц |

8, 32 Кбайт |

Модуль DIP40 |

DS5000T |

до 8, 12 или 16 МГц |

8, 32 Кбайт |

Таймер реального времени |

DS2250 |

до 8, 12 или 16 МГц |

8, 32, 64 Кбайт |

Модуль SIP (SIMM 40) |

DS2250T |

до 8, 12 или 16 МГц |

8, 32, 64 Кбайт |

Таймер реального времени |

Изделия на базе DS5001FP |

|||

DS2251 |

до 12 или 16 МГц |

32, 64, 128 Кб |

Модуль SIP (SIMM 72) |

DS2251Т |

до 12 или 16 МГц |

32, 64, 128 Кб |

Таймер реального времени |

Изделия на базе DS5002FP |

|||

DS2252 |

до 12 или 16 МГц |

32, 64, 128 Кб |

Модуль SIP (SIMM 40) |

DS2252Т |

до 12 или 16 МГц |

32, 64, 128 Кб |

Таймер реального времени |

Особенности структуры МК:

Watchdog Timer

Неприятность может случиться при работе любого процессорного устройства, если в порядок выполнения программы вмешался случайный отказ ("сбой"). При этом программа попадает в ошибочный или запланированный бесконечный цикл. Выйти из этой ситуации поможет специальный дежурный таймер (Watchdog Timer). При переполнении этого таймера происходит внутренняя инициализация процессора, а специальные флаги укажут, по какой причине произошла инициализация.

Генератор случайных чисел.

Процессор DS5002 содержит генератор случайных чисел, который выдает последовательность 8-битных случайных чисел через каждые 160 микросекунд. Он может оказаться полезным в большинстве многоточечных коммуникационных систем с целью обработки столкновений.

Начальная проверка программы

В микроконтроллерах всегда существует неизменная (резидентная) часть программы, которую неплохо было бы проверить в начале работы. Проверять при помощи той же программы - это не проверить ничего, поэтому, начиная с DS5001, введен механизм автоматического вычисления CRC (циклического кода) участка памяти и сравнение его с ранее вычисленным значением. При несовпадении, управление передается встроенной программе загрузчика.

Межпроцессорный обмен.

Очень важным аспектом при составлении многопроцессорных систем является наличие межпроцессорного обмена. Обычно для MCS51 для этого используется последовательный канал. В процессорах DS5001 и DS5002 существуют дополнительно программируемый контроллер байтового обмена. Для его использования внешний процессор присоединяется к выводам портов 0 и 2. Для обеих процессоров (внешнего и внутреннего) появляется независимая возможность обращения к двум регистрам обмена. Протокол обмена совпадают с протоколом микросхемы i8042 фирмы Intel. Возможно также подсоединение устройств прямого доступа (DMA). Интерфейс отключаемый, и эти порты можно использовать обычным для MCS51 способом. При желании можно организовать порт обмена по шине IBM PC с другим аналогичным процессором или с устройствами цифровой обработки сигналов (ЦОС). Например, в микросхемах ЦОС AD21xx требуется начальная загрузка по 8-битному каналу. Поскольку обмен идет с квитированием, то для этой цели удобно воспользоваться имеющейся в DS5000 возможностью, получив, таким образом, изящный обрабатывающий комплекс.

1.5.2. Обеспечение высокой производительности в скоростных микроконтроллерах.

Одной из важных характеристик любой вычислительной системы является быстродействие. Для микроконтроллеров эта характеристика напрямую связана с тактовой частотой, длительностью цикла обращения к памяти, числа циклов в одной команде и набора команд.

В течение 13 лет существования семейства MCS51 увеличения быстродействия добывались простым увеличением максимальной тактовой частоты. Лишь в 1993 году фирма DSC сократила число тактов в цикле и количество циклов в команде. Рассмотрим особенности и разницу временных характеристик стандартных микроконтроллеров фирмы Intel и быстродействующего микроконтроллера DS80C320 фирмы DSC.

Цикл стандартного микроконтроллера длится 12 тактов, и в течении цикла происходит два считывания программной памяти. Цикл DS80C320 длится 4 такта, но за это время происходит только одно считывание. Таким образом, DS80C320 считывает программную память в полтора раза быстрее стандартного процессора. Временные характеристики изображены на рис. 1.9.

<

Номенклатура микроконтроллеров с высоким быстродействием. Это семейство содержит устройства, по внешнему виду и номенклатуре выводов совпадающие с устройствами MCS51, выполненных в тех же корпусах. Выпускаются они фирмой DSC в корпусах DIP40, PLCC44, TQFP44 и PLCC52 и обладают одинаковым увеличением быстродействия за счет уменьшения длительности цикла и лучшей организации внутреннего конвейера. В среднем, вычислительная эффективность процессоров увеличивается в 2,5 раза по сравнению со стандартной, а скорость счета внутренних счетчиков в 3 раза.

Перечень изделий этого семейства, быстродействие и объем внутрикристальной памяти даны в табл. 1.8.

Таблица 1.8

Таблица 2. Изделия семейства High Speed Micro. |

|||

Название |

Тактовая частота |

Объем памяти |

Особенности |

DS80C310 |

до 25 или 33 Мгц |

256 байт |

Упрощенный вариант |

DS80C320 |

до 25 или 33 Мгц |

256 байт |

|

DS80C323 |

до 20 Мгц |

256 байт |

Питание 3 В |

DS87C520 |

до 33 Мгц |

256 + 16К ПЗУ + 1К ОЗУ |

Имеется вариант корпуса с кварцевым окном |

DS87C530 |

до 33 Мгц |

256 + 16К ПЗУ + 1К ОЗУ |

Таймер реального времени, энергонезависимая память |

Команды MCS51 состоят из одного, двух или трех байт. При выполнении команды процессор сначала считывает байты этой команды, а потом может несколько раз считать первый байт следующей. Во всех командах DS80C320 уменьшено число таких бесполезных считываний. Таким образом, микропроцессор DS80C320 быстрее стандартного 18051 в среднем в 2.5 раза. В табл. 1.10 приведены эквивалентные частоты этих двух процессоров. Максимальная тактовая частота DS80C320 и других процессоров этого семейства - 33 Мгц. Минимальная частота ничем не ограничена, поскольку все микропроцессоры DSC являются полностью статическими.

Таблица 1.10.

Сравнение тактовых частот для процессоров одинаковой производительности

СТАНДАРТНЫЙ 8051 |

DS80C320 |

11,0592 Мгц

16 Мгц

20 Мгц

24 Мгц

33 Мгц

44 Мгц

62.5 Мгц

82.5 МГц, |

4.4 Мгц

6.4 Мгц

8 Мгц

9.6 Мгц

13.2 Мгц

16 Мгц

25 Мгц

33 Мгц |

1.5.3. Организация памяти скоростных контроллеров.

Микроконтроллеры MCS51 имеют гарвардскую архитектуру, которая подразумевает целевое разделение памяти. Адресуемая косвенно и непосредственно внутренняя регистровая память (Scratchpad Меmory) имеет максимально возможный объем 256 байт и для скоростного семейства ничем не отличается от стандартной. В микросхемах DS87C5xx имеется также внутренняя программная память и внутренняя память данных (обращение по инструкциям MOVX).

Внутренняя программная память объемом 16 Кбайт выполнена по технологии перепрограммируемого ПЗУ (EPROM). В зависимости от используемого корпуса, она может быть программируемой однократно или стираемая ультрафиолетовыми лучами. Для предотвращения несанкционированного доступа при программировании разрешено три уровня защиты. Объем внутренней памяти может быть ограничен программно, несмотря на то, что физический ее объем остается прежним. Разрешены следующие устанавливаемые в любое время границы: 0, 1, 2, 4, 8, 16, 32 и 64 Кбайта. При обращении к программной памяти ниже установленной границы происходит считывание внутренней памяти (даже за пределами 16 Кбайт), в противном случае происходит считывание внешней памяти с использованием портов 0 и 2.

Внутренняя память данных имеет объем 1 Кбайт, расположена с нулевого адреса и может быть отключена или включена на все адресное пространство. В последнем случае реально считывается и записывается только первые 1 Кбайт памяти и один системный байт, несущий информацию о используемой защите программирования

Обращение к внешней памяти данных по умолчанию происходит за один цикл (два цикла на команду MOVX). При частоте 33 Мгц требуется микросхемы памяти с временем доступа менее 80 нс. Имеется механизм, позволяющий увеличить длительность сигналов RD и WR в интервале с 4 до 28 машинных циклов. Это обеспечивает обращение по команде MOVX к медленной памяти и различным по скорости устройствам ввода/вывода. Длительность задается программно в любой момент времени.

1.5.4. Возможности скоростных контроллеров.

Перечень и возможности этих моделей даны в табл. 1.11.

Таблица 1.11.

Возможности скоростных контроллеров фирмы Dallas

Тип контроллера |

DS80C310 |

DS80C320 |

DS80C323 |

DS83C520 |

DS87C520 |

DS67C530 |

Внутреннее ПЗУ |

- |

- |

- |

16 Кбайт Маска |

16Кбайт EPROM |

16Кбайт EPROM |

Регистровое ОЗУ |

256 байт |

256 байт |

256 байт |

256 байт |

256 байт |

256 байт |

Внутренне ОЗУ (MOVX) |

1 Кбайт |

1 Кбайт |

1 Кбайт |

|||

Последовательный канал |

1 |

2 |

2 |

2 |

2 |

2 |

Внешние прерывания |

6 |

6 |

6 |

6 |

6 |

6 |

Дежурный таймер (WatchDog Timer) |

+ |

+ |

+ |

+ |

+ |

|

Реакция на пропадание питающего напряжения |

+ |

+ |

+ |

+ |

+ |

|

Указатели DPTR |

2 |

2 |

2 |

2 |

2 |

2 |

16-битные таймеры |

3 |

3 |

3 |

3 |

3 |

3 |

Управление потреблением |

|

+ |

+ |

+ |

||

Встроенный генератор |

+ |

+ |

+ |

+ |

+ |

|

Управление потреблением |

|

+ |

+ |

+ |

||

Таймер реального времени |

|

+ |

||||

Энергонезависимая память |

|

+ |

1.6. ОДНОКРИСТАЛЬНЫЕ МИКРОКОНТРОЛЛЕРЫ СЕРИИ PIC

Первые микроконтроллеры компании MICROCHIP PIC16C5x появились в конце 80-х годов и благодаря своей высокой производительности и низкой стоимости составили серьёзную конкуренцию производимым в то время 8-разрядным МК с CISC-архитектурой.

Первое, что привлекает внимание в PIC-контроллерах — это простота и эффективность. В основу концепции PIC, единую для всех выпускаемых семейств, была положена RISC-архитектура с системой простых однословных команд, применение встроенной памяти программ и данных и малое энергопотребление.

Система команд базового семейства PIC165x содержит только 33 команды. Как ни странно, и это сыграло свою роль в популяризации PIC-контроллеров. Все команды (кроме команд перехода) выполняются за один машинный цикл (или четыре машинных такта) с перекрытием по времени выборок команд и их исполнения, что позволяет достичь производительности до 5 MIPS при тактовой частоте 20 МГц.

Микроконтроллеры PIC имеют симметричную систему команд, позволяющую выполнять операции с любым регистром, используя любой метод адресации. Правда, разработчики MICROCHIP так и не смогли отказаться от любимой всеми структуры с регистром-аккумулятором, необходимым участником всех операций с двумя операндами. Зато теперь пользователь может сохранять результат операции на выбор, где пожелает, в самом регистре-аккумуляторе или во втором регистре, используемом для операции. В настоящее время MICROCHIP выпускает четыре основных семейства 8-разрядных RISC-микроконтроллеров, совместимых снизу вверх по программному коду:

базовое семейство PIC15Cx с 12-разрядными командами, простые недорогие микроконтроллеры с минимальной периферией;

PIC12Cxxx с 12-разрядными командами со встроенным тактовым генератором, выпускаемые в миниатюрном 8-выводном исполнении. Не так давно был анонсирован очередной такой “малыш” c внутренним 8-разрядным 4-канальным АЦП;

Mid-range PIC16x/7x/8x/9x с 14-разрядными командами. Наиболее многочисленное семейство, объединяющее микроконтроллеры с разнообразными периферийными устройствами, в число которых входят аналоговые компараторы, аналогово-цифровые преобразователи, контроллеры последовательных интерфейсов SPI, USART и I2C, таймеры-счётчики, модули захвата/сравнения, широтно-импульсные модуляторы, сторожевые таймеры, супервизорные схемы и так далее;

High-end PIC17C4x/5xx высокопроизводительные микроконтроллеры с расширенной системой команд 16-разрядного формата, работающие на частоте до 33 МГц, с объёмом памяти программ до 16 Кслов. Кроме обширной периферии почти все микроконтроллеры этого семейства имеют встроенный аппаратный умножитель 8х8, выполняющий операцию умножения за один машинный цикл.

Большинство PIC-контроллеров выпускаются с однократно программируемой памятью программ OTP с возможностью внутрисхемного программирования или масочным ROM. Для целей отладки предлагаются версии с ультрафиолетовым стиранием, надо признать, не очень дешёвые. Полное количество выпускаемых модификаций PIC-контроллеров составляет порядка пятисот наименований. Как не без основания утверждает MICROCHIP, продукция компании перекрывает весь диапазон применений 8-разрядных микроконтроллеров.

Особый акцент MICROСHIP делает на максимально возможное снижение энергопотребления для выпускаемых микроконтроллеров. При работе на частоте 4 МГц PIC-контроллеры, в зависимости от модели, имеют ток потребления меньше 1,5 мА, а при работе на частоте 32,768 КГц — ниже 15 мкА. Поддерживается “спящий” режим работы. Диапазон питающих напряжений PIC-контроллеров составляет 2,0...6,0 В.

В настоящее время готовится к запуску в производство новое пятое семейство PIC-контроллеров PIC18Cxxx. Новые микроконтроллеры будут иметь расширенное RISC-ядро, оптимизированное под использование нового Си-компилятора, адресное пространство программ до 2 Мбайт, до 4 Кбайт встроенной памяти данных и производительность 10 MIPS.

Из программных средств отладки наиболее известны и доступны различные версии ассемблеров, а также интегрированная программная среда MPLAB. Российские производители программаторов и аппаратных отладочных средств также уделяют внимание PIC-контроллерам. Выпускаются как специализированные программаторы, такие как PICPROG, программирующие почти весь спектр PIC-микроконтроллеров, так и универсальные: UNIPRO, СТЕРХ, поддерживающие наиболее известные версии PIC.

1.6.1. RISC микроконтроллеры типа PIC16C5X

МК PIC16C5X, производимые фирмой Microchip Tecnology относятся к семейству КМОП микроконтроллеров с внутренним ПЗУ, которые отличаются низкой стоимостью, высокой производительностью, 8-битовыми операциями с данными. Они основаны на RISC архитектуре и программируются всего через 33 команды, шириной в одно слово ПЗУ. Все команды выполняются за один цикл (200нс). PIC16C5X имеют характеристики, на порядок превосходящие конкурирующую продукцию, но находятся в той же ценовой категории. Расширенные двенадцатибитные команды приводят к сжатию кода до 2:1 по сравнению с 8-битными микроконтроллерами этого же класса. Простота изучения и применения команд экономит время разработчика.

PIC16C5X имеют встроенные устройства, присущие большинству прикладных систем, что позволяет снизить стоимость, потребляемую мощность и увеличить надежность конечного устройства. Например, встроенная схема сброса и запуска генератора позволяют избавиться от внешних RC схем. Предлагается четыре типа встроенных генераторов на выбор, включая экономичный LP (Low Power) и дешевый RC генераторы. Экономичный режим SLEEP, Watchdog таймер и устройство защиты кода программы снижают стоимость и увеличивают мощность плюс надежность вашей системы. Микросхемы с ультрафиолетовым стиранием идеальны для процесса отработки программы. Одновременно существуют однократно программируемые (OTP) кристаллы. Здесь разработчик может извлечь полное преимущество из сочетания низкой цены и гибкости OTP версий.

Серия PIC16C5X подходит для широкого спектра приложений от схем высокоскоростного управления автомобильными и электрическими двигателями до экономичных удаленных приемопередатчиков, показывающих приборов и связных процессоров. Наличие ПЗУ позволяет подстраивать параметры в прикладных программах (коды передатчика, скорости двигателя, частоты приемника и т.д.).

Малые размеры корпусов, как для обычного, так и для поверхностного монтажа, делает эту серию микроконтроллеров пригодной для портативных приложений. Низкая цена, экономичность, быстродействие, простота использования и гибкость ввода/вывода делает серию PIC16C5X привлекательной даже в тех областях, где ранее не применялись микроконтроллеры. Например, таймеры, замена жесткой логики в больших системах, сопроцессоры.

Устройства серии PIC16C5X имеют большой выбор ПЗУ и ОЗУ разных размеров, разное количество линий ввода/вывода, различные виды возбуждения генераторов, разную скорость, климатику и типы корпусов. Из четырех кристаллов PIC16C5x можно выбрать устройство с подходящими ПЗУ/ОЗУ и конфигурацией ввода/вывода.

Таблица 1.12

Название |

ПЗУ |

ОЗУ* |

Ввод/Вывод+ |

Тип корпуса |

PIC16C54 |

512*12 |

32*8 |

13 |

CERDIP-18 |

PIC16C55 |

512*12 |

32*8 |

21 |

CERDIP-28 |

PIC16C56 |

1K*12 |

32*8 |

13 |

CERDIP-18 |

PIC16C57 |

2K*12 |

80*8 |

21 |

CERDIP-28 |

* включая регистры специального назначения

+ включая линию вход RTCC счетчика.

Устройства с ультрафиолетовым стиранием удобно использовать в прототипных и опытных партиях. Конфигурация генератора ("RC", "XT", "HS", "LP") программируется самим пользователем на UF EPROM. При UF стирании или по умолчанию устанавливается тип "RC". В зависимости от выбранного типа генератора и частоты, рабочее напряжение питания должно быть в том же диапазоне, что будет и в будущем устройстве на OTP кристалле (если OTP предполагается использовать).